受限于基础物理极限,硅基晶体管的尺寸已无法继续按比例缩小,越来越难以满足人工智能等前沿领域日益增长的计算需求。为此,研究人员正积极开发新型沟道材料,并探索替代传统冯·诺依曼架构的方案,以期取得能够延续甚至超越摩尔定律的突破性进展。然而,基于二进制电路的系统中最关键的挑战之一仍然是功能单元之间及内部连线的片上互连。随着晶体管密度的持续提升,互连所占用的面积预计将超过逻辑单元,这对进一步的微缩与集成构成了重大障碍。多值逻辑(MVL)因其更高的计算效率和数据吞吐能力,被认为是缓解这一问题的有前景的方案。与二进制逻辑不同,MVL在单个逻辑单元内包含多个逻辑状态,能够执行更复杂的运算,从而从根本上降低功耗和芯片面积。传统硅基金属氧化物半导体场效应晶体管(MOSFET)是为二进制逻辑设计的,其固有的电学特性和工艺限制阻碍了MVL所需的多个稳定电压状态的实现。

半导体型单壁碳纳米管(s-SWCNT)凭借其一维超薄结构和极高的载流子迁移率,被认为是亚纳米超制程技术节点的重要候选材料。然而,如何将这些固有优势转化为电可寻址的MVL器件,仍然是一个挑战。这一困难主要源于在限域体积内定义和稳定多个不同的电导状态,并将其可靠地耦合到输出信号的问题,从而限制了它们在复杂计算系统中的潜在应用。

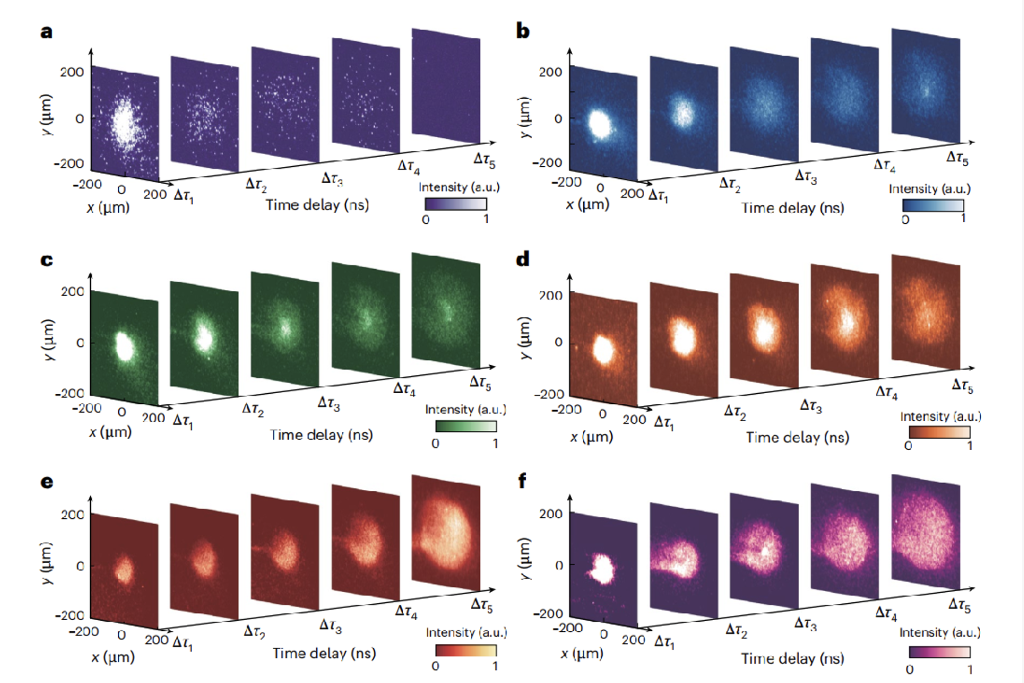

针对上述问题,中国科学院苏州纳米所康黎星研究员及合作者提出了一种由s-SWCNT和乙酰丙酮钇(Y(acac)3)组成的一维同轴异质结构,并将其用作晶体管的沟道材料。该晶体管表现出多个电阻态,适用于MVL电路。该方法实现了s-SWCNT内部均匀且稳定的掺杂,有效缓解了由于表面悬挂键导致的金属-半导体接触退化和载流子散射。s-SWCNT一维中空腔体的径向限域作用诱导了封装Y(acac)3分子的形变。这一解释与高角环形暗场扫描透射电子显微镜图像中观察到的衬度特征一致,并得到了光谱学证据和密度泛函理论计算的进一步支持。这种形变增强了分子的极化率,从而在外电场下产生更显著的极化响应。通过这一机制,在晶体管的工作电压范围内实现了沟道载流子的协同捕获与释放,进而在同一器件内产生稳定的多电阻态。基于这一特性制备的三元逻辑电路对输入信号具有选择性,能够准确识别输入信号的最大值或最小值并产生相应的输出。此外,还展示了三元权重网络(TWN)在神经形态计算中的潜力。进一步地,通过实验和理论研究,将这一概念推广到由其他金属乙酰丙酮配合物与s-SWCNT构成的一维异质结构体系。与传统的多值逻辑方案相比,该工作避免了复杂的能带工程或多层堆叠,更有利于大规模集成,并为理解一维异质结构内的构效关系以及实现三元逻辑晶体管提供了新的视角。

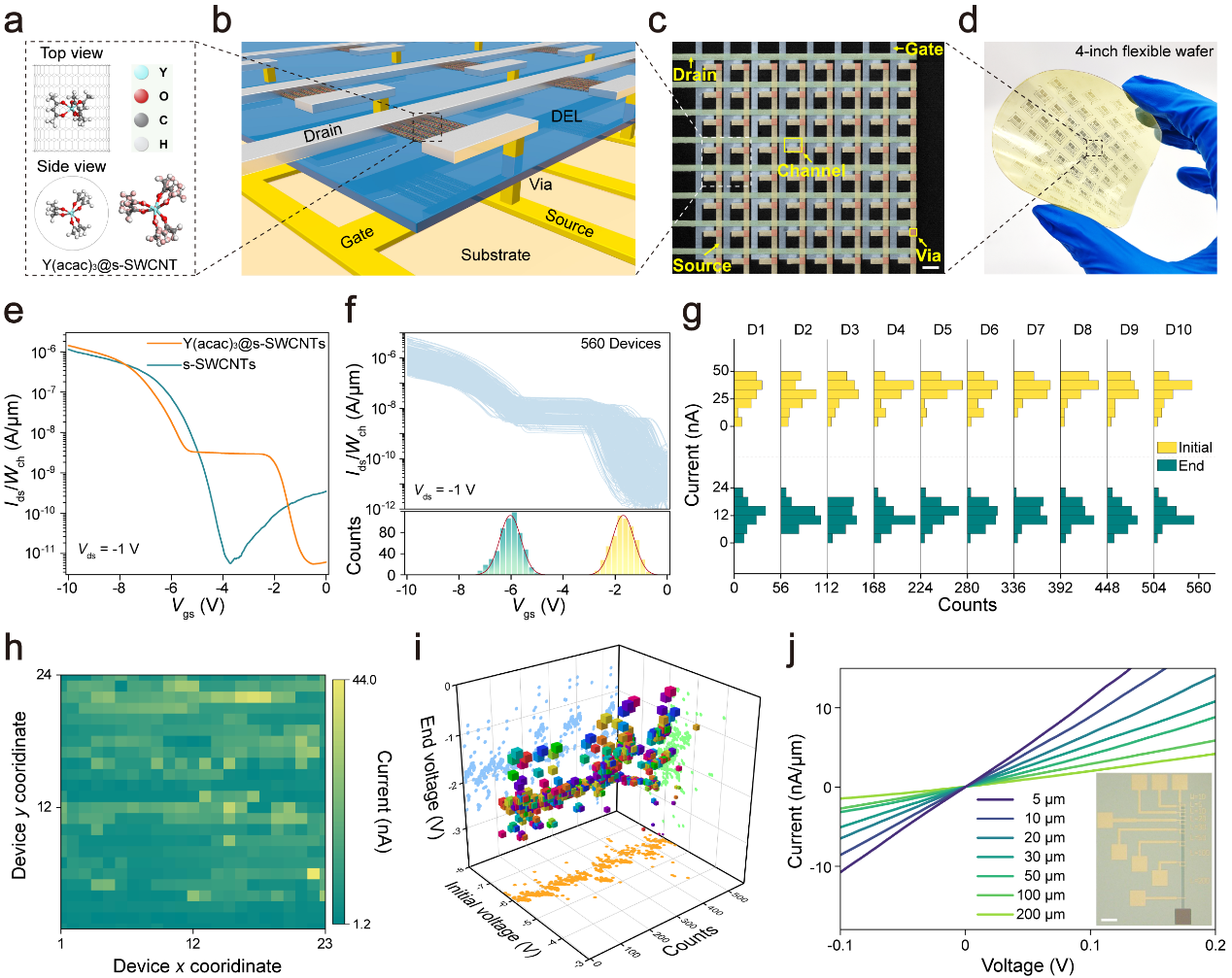

图1 基于Y(acac)3@s-SWCNT异质结构的柔性晶圆制备过程及其电学均匀性表征

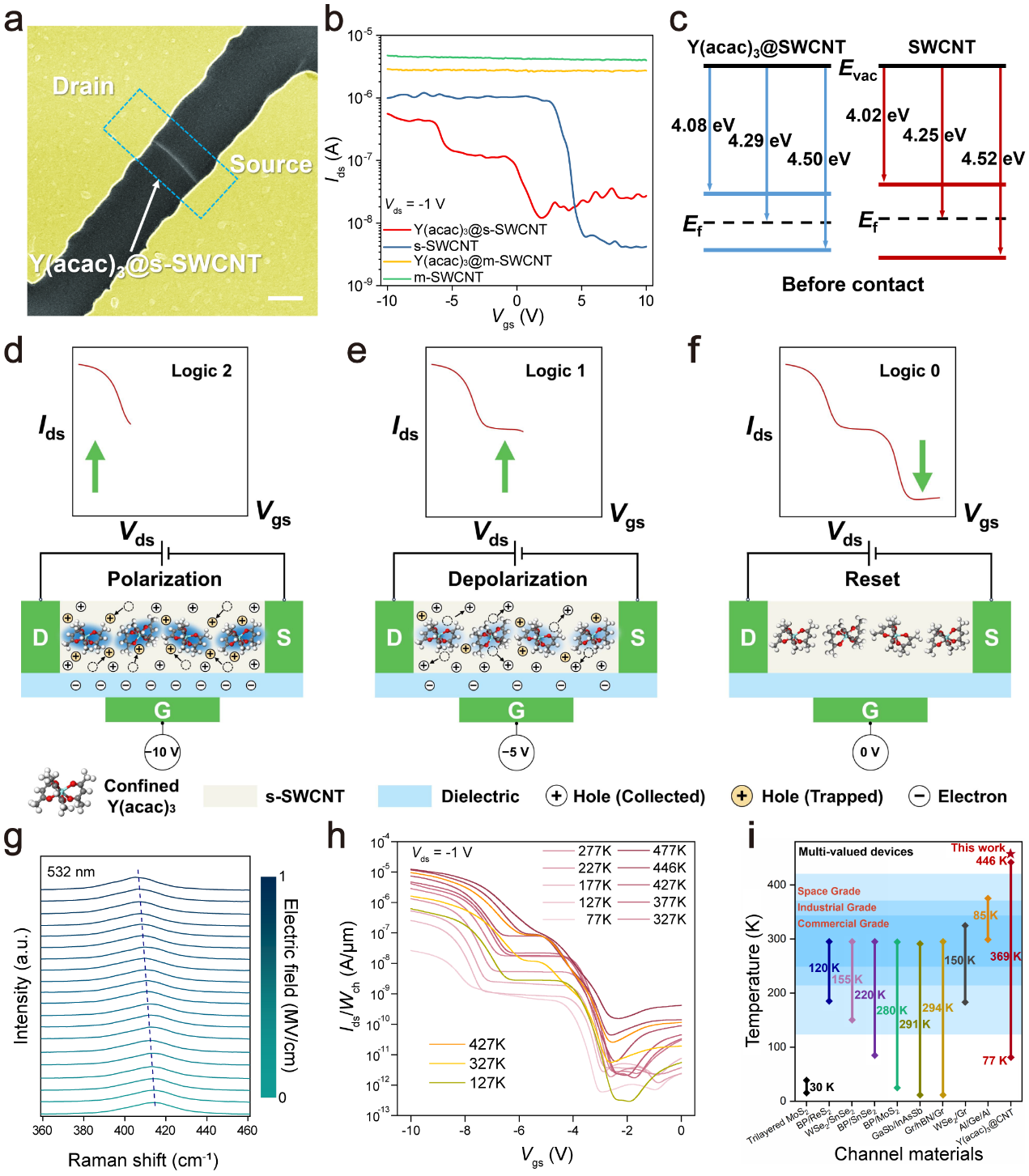

图2 Y(acac)3@s-SWCNT异质结构实现ternary逻辑功能的物理机制

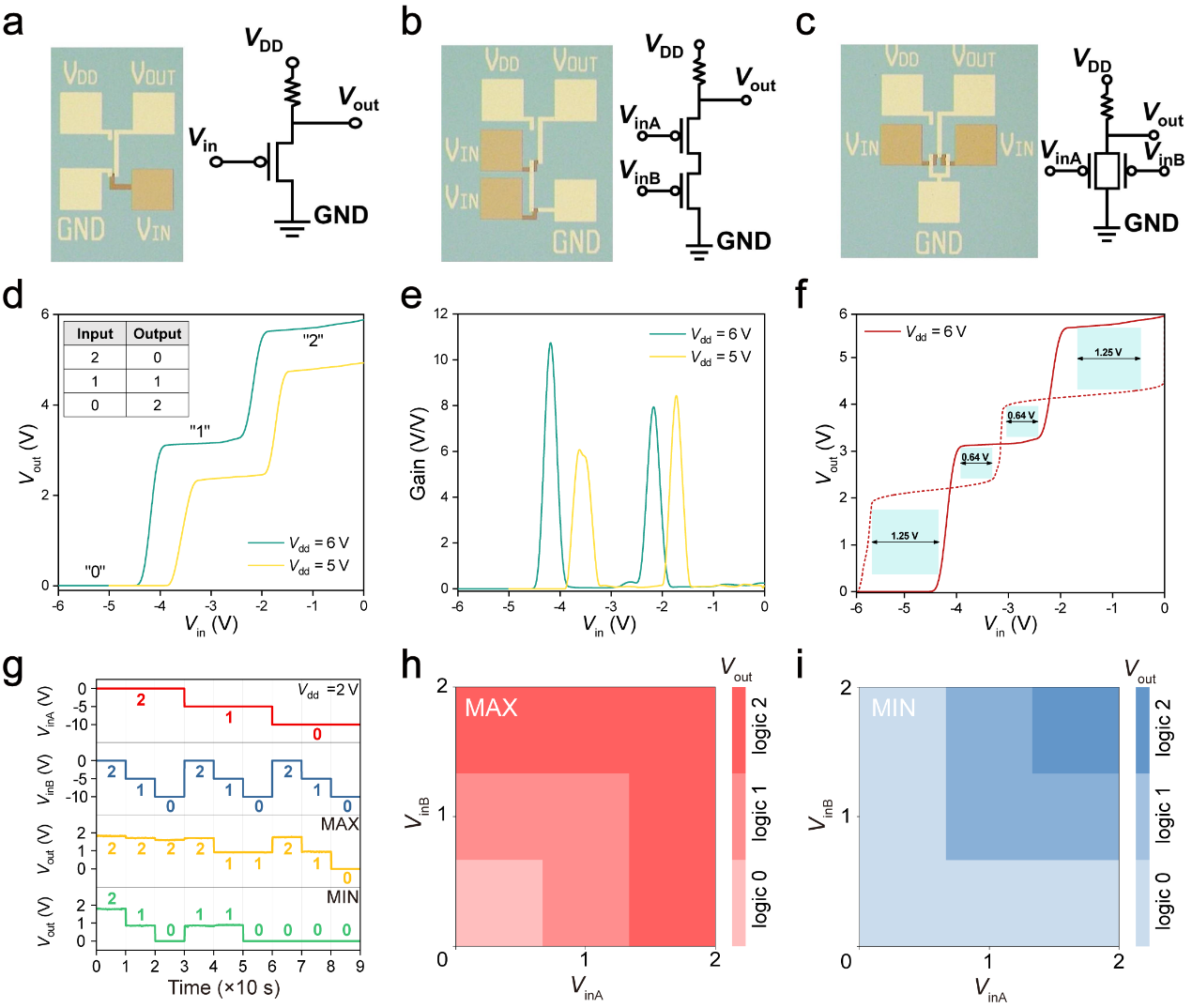

图3 基于Y(acac)3@s-SWCNT ternary晶体管的逻辑门电路设计及其电压传输特性曲线

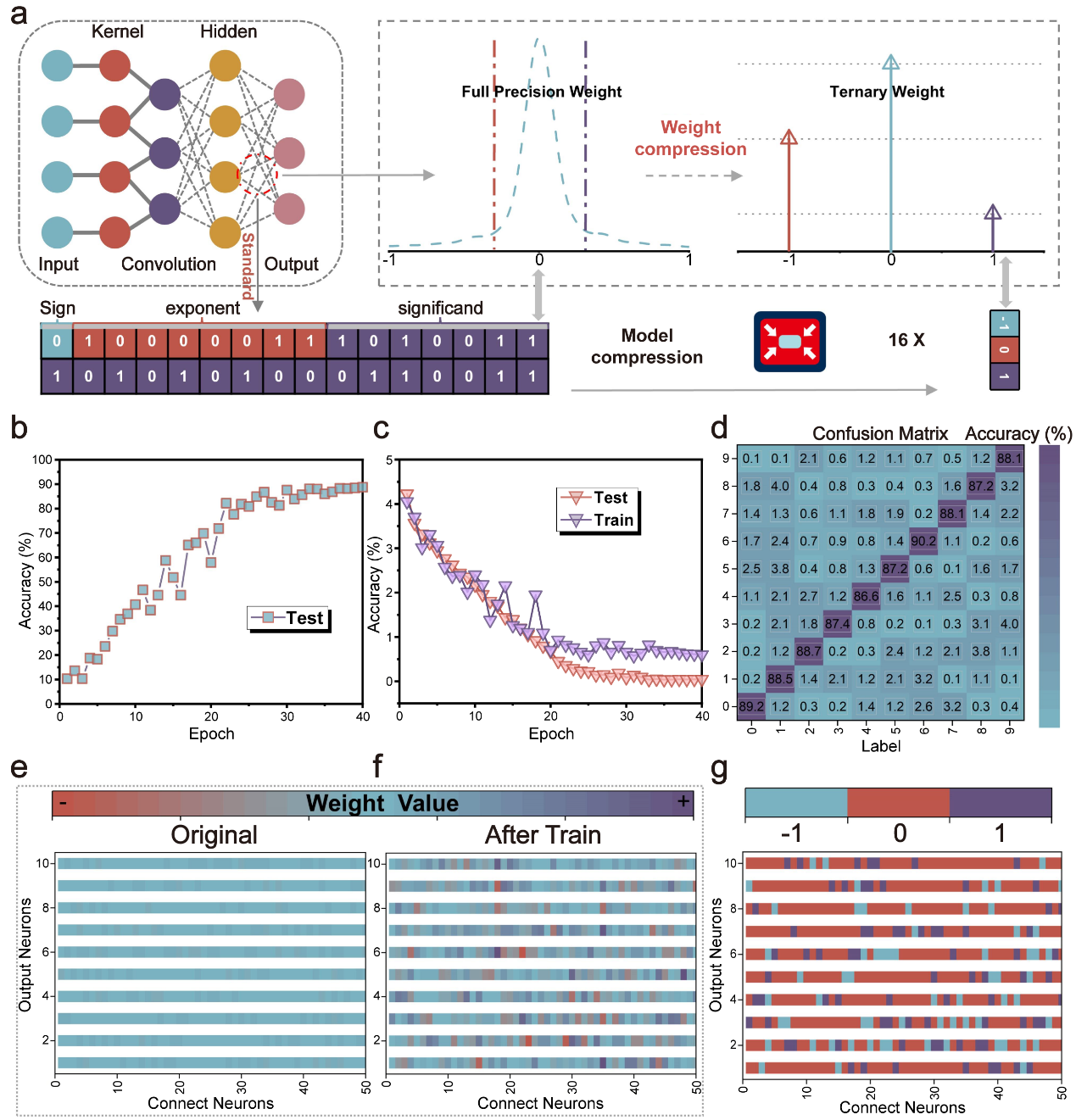

图4 Ternary权重网络(TWNs)在神经形态计算中的应用

相关成果以Filled carbon nanotube ternary transistors为题发表于Advanced Materials。中国科学院苏州纳米所博士生滕宇、姚建,博士后王琦男为论文共同第一作者,中国科学院苏州纳米所康黎星研究员、西交利物浦大学赵春教授和新加坡国立大学Mario Lanza教授为共同通讯作者。该研究获得了国家自然科学基金、中国科学院“率先行动”引才计划、江苏省前沿技术研发计划等项目的经费支持,以及中国科学院苏州纳米所纳米真空互联实验站(Nano-X)和纳米加工平台的技术支持。

论文链接