芯观点──聚焦国内外产业大事件,汇聚中外名人专家观点,剖析行业发展动态,带你读懂未来趋势!

芯片之外,Chiplet(“小芯片”)正逐渐进入行业视野。

小芯片并不是传统意义上的“芯片”。事实上,“小芯片”可以说是一种高级封装技术,是一种绕过摩尔定律的思维:我们不一定非要把芯片缩得越来越小,而是把芯片的集成电路板甚至是主机变得越来越小。它的出现有何意义,又将给行业带来哪些改变?

颠覆时代?

众所周知,集成电路行业有着这样一条金科玉律——摩尔定律,即集成电路上可容纳的晶体管数目,每隔18-24个月便会增加一倍,性能也将提升一倍。按照摩尔定律,几十年来,我们都在追求在更小的芯片上塞满更多的晶体管,几乎两年翻一番。但物理学总是难以违逆的,摩尔定律目前已经持续逼近极限。在此背景下,集成电路厂商正在尝试不依赖制程工艺进步,转而在材料、封装上下功夫,Chiplet即是典型技术之一。而“小芯片”的概念很有可能以逆转思维颠覆时代。

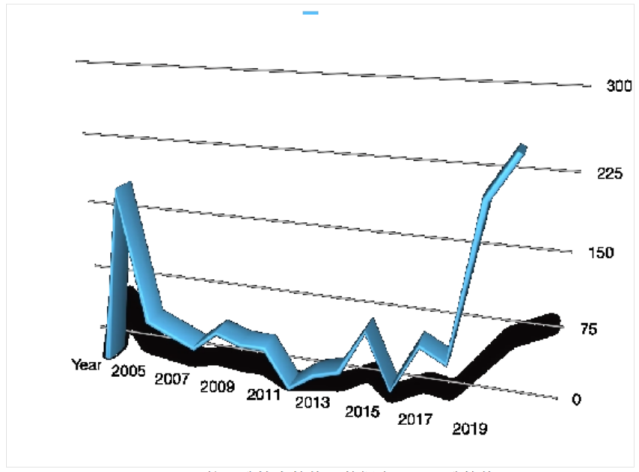

图:根据AMD公布的内部估计,摩尔定律正在下滑

事实上,小芯片也并不是什么新鲜的事物。根据谷歌搜索趋势,小芯片作为搜索术语可追溯到2004年,但这个热情很快就消退,直到2019年才开始真正上涨。

图源:“chiplet”的谷歌搜索趋势

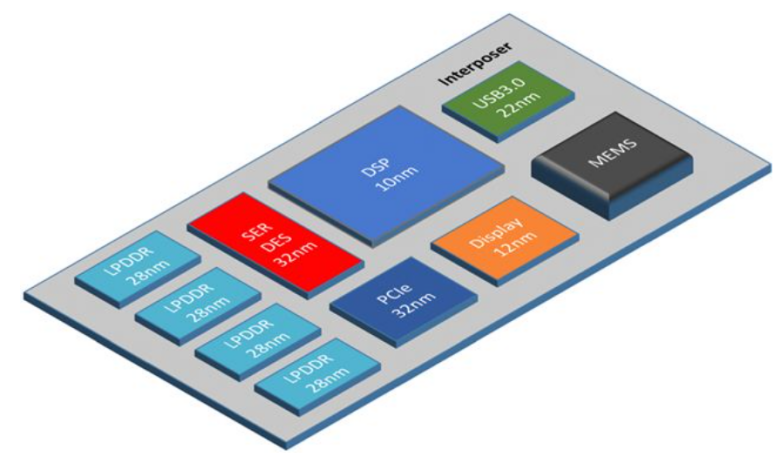

Chiplet是把不同功能的芯片封装在一块PCB上面,通过这样的做法来提高系统的集成度。它的目标是通过在 IC 封装中集成预先开发的芯片来减少产品开发时间和成本。以前芯片由多个IP核心集成后统一封装成单片芯片,而小芯片方法可将来自不同公司设计和封装的小芯片组合在一起,从而构建更为高效和经济的芯片系统。

具体来看,使用chiplet至少具备两大优点:一是提升了良率,如果使用大芯片,在芯片的晶圆面积上只要出现瑕疵,那么整个芯片就有了瑕疵,无法作为良品使用;但是如果把同样面积的芯片拆分为多个chiplet,那么出现瑕疵的话就仅仅是单个有瑕疵的chiplet无法使用,其他chiplet则不受影响,这样就提升了良率,而这对于良率存在挑战的先进半导体工艺至关重要。二是,Chiplet另外的潜力在于可以实现更灵活的异构集成,在同一封装系统中不同的chiplet可以使用不同的半导体工艺实现,从而进一步降低成本(例如某些对于逻辑性能需求不高的模组可以使用成熟工艺)并提升性能。

无疑,在“后摩尔定律”时代,小芯片可作为一种解方,可能带给从上游IC设计、EDA 工具、制造工艺、先进封测等各个产业链环节颠覆式的改变,是IC业继续发展最有效的手段。

巨头入局

也正是基于上述优点,小芯片持续受到市场的关注,成为AMD、英特尔、台积电、Marvell、Cadence等芯片巨头为摩尔定律续命的共同选择之一。而2D、2.5D、3D 封装等技术则是达成 Chiplet 的解决方案。

2018年底,Intel首次公开名为“Foveros”的全新3D芯片封装技术。通过Foveros,英特尔将能够整合各种芯片叠加在一起,包括CPU,内存和其他芯片,而无需担心各自的底层制造技术。

利用这项技术,英特尔推出了代号为“Lakefield”的 3D CPU 平台,将一个 10 纳米处理器内核与四个 22 纳米处理器内核结合在一个封装中。在研发方面,英特尔正在开发其他基于小芯片的产品,包括 GPU。

AMD 也基于这个概念推出了多芯片处理器。AMD第二代EPYC服务器处理器Ryzen采用小芯片设计,将先进的台积电7nm工艺制造的CPU模块与更成熟的格芯12/14nm工艺制造的I/O模块组合,7nm可满足高算力的需求,12/14nm则降低了制造成本。同时,采用更成熟制程的I/O模块还有助于整体良率的提升。2020年的最后一天,AMD向美国专利商标局提交了一项新专利,勾勒了未来的GPU小芯片设计。

今年5月三星宣布其2.5D封装技术Interposer-Cube4(I-Cube4)完成开发。三星的I-Cube4同样是一种异构集成技术,可以将一个或多个逻辑芯片或HBM通过中介层集成在一个芯片里,有望应用于HPC、AI、5G和数据中心等领域。

其它代工厂以及 OSATs(进行IC封装和测试的公司)也正开发小芯片策略。例如,台积电正在开发一种称为集成芯片系统 (SoIC) 的技术。SoIC 为在封装中集成具有不同工艺节点的较小芯片铺平了道路。SoIC 采用先进的芯片堆叠技术,使客户能够开发类似 3D 的架构。堆叠技术是使用芯片键合完成的,它可以将两个芯片键合在一起或将一个芯片键合到一个芯片上。该方案可以实现将几种不同类型的芯片(例如处理器、内存或传感器)堆叠和链接到一个封装实体之中,因此得到的芯片尺寸更小,性能更强,能耗也更低。目前台积电的SoIC已能做到12层堆栈(每一层是50微米,等同于头发的50%,头发是100微米)。

此外,格芯、联电和其他公司也在开发类似的晶圆键合技术,有望实现新型芯片。

值得关注的是,半导体领军人物蒋尚义同样倾心于Chiplet先进封装。去年12月,蒋尚义回归中芯国际,主要负责公司先进封装尤其是Chiplet封装技术。在接受采访中,蒋尚义透露,自己执着于追求先进封装、小芯片等系统整合的技术,本次回到中芯国际的目的是协助中芯国际成为世界一流公司,以及在中芯国际实现其自身的技术追求。

大陆封测龙头长电科技面向Chiplet异构集成应用则推出了XDFOI全系列的解决方案,包括2D chiplet、2.5D chiplet、3D chiplet等,可灵活实现异构集成。

仍存挑战

虽然有不少公司已经使用小芯片开发了多芯片设计,但其实开发这些产品仍存挑战。

首先,市场上没有单一的标准芯片到芯片互连或接口解决方案。如今,现在主要有两种小芯片die-to-die接口技术方案,即 AIB 和 XSR。其中,AIB是英特尔推出的一种在小芯片之间传输数据的接口方案和互连标准。多年来,英特尔一直在生产带有AIB接口的产品,在其Stratix 10 FPGA上就使用了AIB接口来集成多种不同的小芯片。由OIF设计的通用电气 I/O (CEI) 112G XSR(超短距)接口可用于小芯片和光学引擎。

但AIB和XSR并不适合所有应用程序。为此,开放域特定架构组织(ODSA)正在定义另外两个接口—线束 (BoW) 和 OpenHBI。从目前的发展来看,每种技术都有自己的优点,但行业还未能围绕一种标准统一起来。

其次,组装问题、设计工具支持、测试和良率,也是小芯片要面临的挑战。就以良率为例,封装需要裸片具有适当的良率,也被称为良品白片。封装中有一个坏晶粒就可能导致产品或系统故障。再进一步探讨,如果封装失败,那么最大的问题便是谁来负责,是芯片供应商、IP 供应商还是封装厂?这都是摆在现实的问题。

再者,由于缺乏生态系统支持等问题,小芯片的采用在业界受到了限制。毕竟并非所有公司都有内部组件,有一些是能够获得的,还有一些则还未准备好。当前企业面临的挑战是找到必要的零件并将其集成,而这将花费不少时间和资源。

还有一个关键是散热问题,当芯片堆栈越来越多,中间芯片的散热要如何克服,也成为材料与制程再创新的重点研发方向,攻克之路还有很多难题需要面对。

当然这些挑战行业也正抓紧克服,随着时间的推移,小芯片将不断发展。市场研究认为,“小芯片”正被更高级和高度集成的半导体设备采用。例如,微处理器(MPU),片上系统(SOC)设备,图形处理单元(GPU)和可编程逻辑设备(PLD),尤其MPU是最受欢迎的。

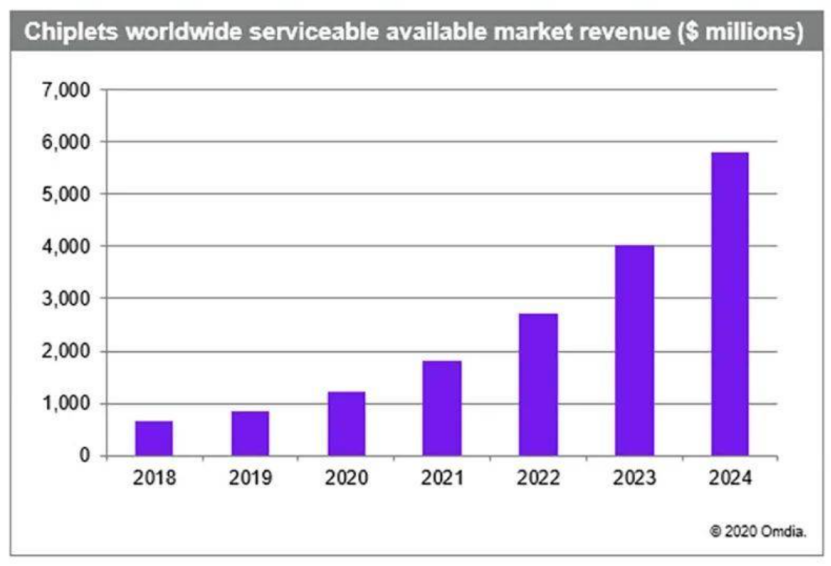

知名市场研究机构Omdia预测,小芯片将在2024年全球市场规模扩大到58亿美元,较2018年的6.45亿美元增长9倍。而长远来看,2035年小芯片市场规模有望增至570亿美元。

图:2018-2024年全球小芯片市场收入(来源:Omdia)

Omdia认为,“小芯片”将在未来4年内成为集成了图形、安全引擎、人工智能(AI)加速、低功耗物联网(IoT)的应用处理器,这将是其58亿美元市场的最重要因素。

知名业内专家莫大康认为,Chiplet的出现,也能够为半导体产业带来新的机会。他提到,“Chiplet的迭代周期远低于ASIC,可提升晶圆厂和封装厂的产线利用率。与此同时,Chiplet技术也有助于建立可互操作的组件、互连、协议和软件生态系统。”

但是,业内也有声音认为小芯片将不会占据主导地位。它也不会替代传统的SoC,毕竟没有一项技术能满足所有需求,所以多架构依然有发展空间。

英特尔工艺产品集成总监Ramune Nagisetty提到:“设备的类型和数量正在不断增加。我认为并非所有产品都会采用基于小芯片的方法。在某些情况下,单片模具将是成本最低的选择。但是对于高性能产品,可以肯定地说,小芯片方法将成为一种规范,虽然这种技术还未成熟。”

结语:从目前的发展来看,单靠小芯片来延续摩尔定律几乎不现实,但值得肯定的是,得益于其集成、灵活、经济等优势,小芯片的市场前景依旧可期。在“后摩尔时代”,小芯片能掀起多大的浪花?这是小芯片面临的挑战,也是“后摩尔时代”不确定性的魅力所在,而此刻还仅是开端。(校对/holly)