上海浦东新区纳贤路60号——卧虎藏龙之地。

在一片青绿的掩映之下,红色大楼里隐藏着中国集成电路的超强大脑——国产EDA行业的领军企业之一芯和半导体。

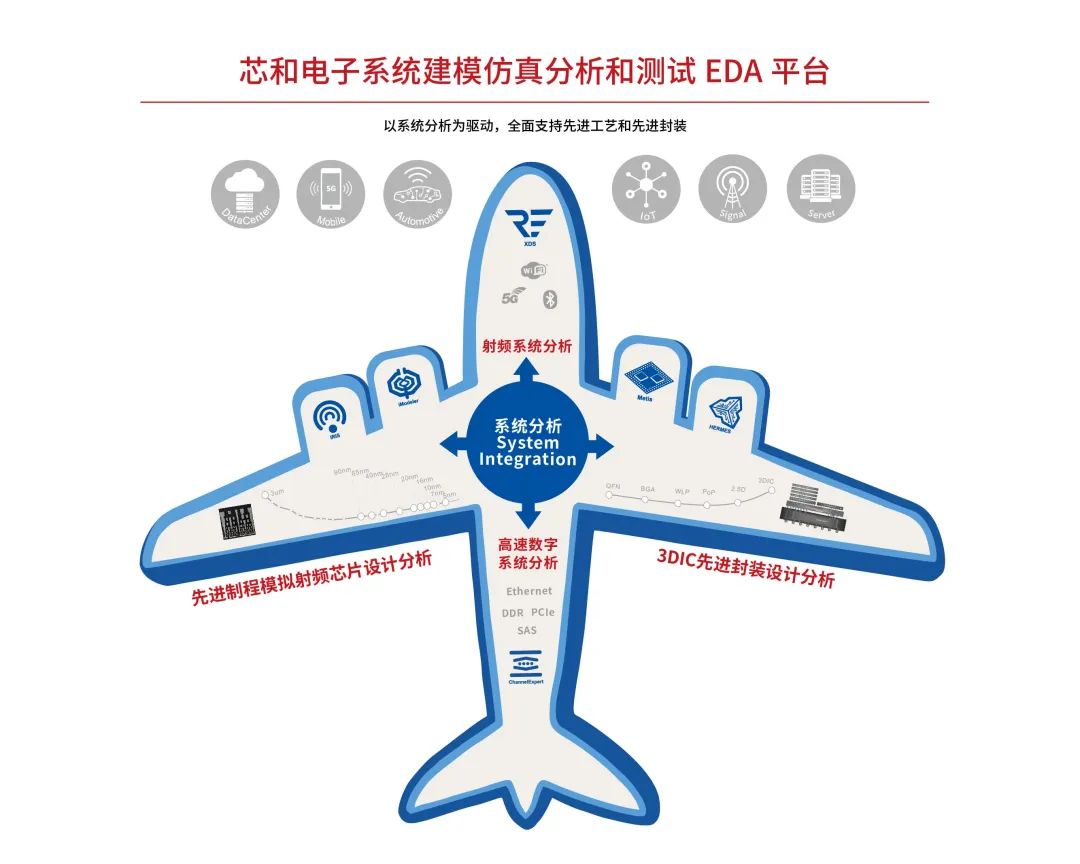

创建于2010年的芯和半导体可提供覆盖IC设计、封装到系统的全链仿真EDA解决方案,致力于赋能和加速新一代高速高频智能电子产品的设计。

芯和半导体自主知识产权的EDA产品和方案在半导体先进工艺节点和先进封装上不断得到验证,并在5G、智能手机、物联网、人工智能和数据中心等领域得到广泛应用,有效联结了各大IC设计公司与制造公司。

芯和半导体同时在全球5G射频前端供应链中扮演重要角色,通过自主创新的无源芯片IPD平台和系统级封装设计平台为手机和物联网客户提供射频前端滤波器等芯片和模组,并被全球著名的半导体分析机构Yole列入全球IPD设计的主要供应商之一(Dedicatede IPD Filter Design House)。

公司联合创始人代文亮,在上海交通大学获得博士学位,曾任Cadence上海全球研发中心高级技术顾问,现任工信部国家信息技术紧缺人才培养工程专家(集成电路类)、中国电子科技集团公司微系统客座首席专家。

在半导体行业处于风口浪尖的关键时刻,代文亮博士接受了海望联盟的专访,以他特有的“川普”向我们讲述了芯和半导体从无人喝彩到厚积薄发再到如今身处浪潮之巅的不凡历程。

代文亮 博士

芯和半导体科技(上海)有限公司 联合创始人、高级副总裁;上海交通大学博士,高速模拟射频集成电路设计和3DIC微系统封装集成领域知名EDA专家,现任工信部国家信息技术紧缺人才培养工程专家(集成电路类),现任中国电子科技集团公司微系统客座首席专家,IEEE TMTT、 IEEE TAP、DAC等国际期刊和会议的常规审稿人,曾任Cadence上海全球研发中心高级技术顾问。2013年获江苏省吴江市“柔性引进”人才;2015年江苏省“六大人才高峰”第十二批高层次人才;2016年度“中国芯-领军风云榜”十大领军人物;2020年获“上海市科技进步”一等奖(No.3)。已累计获得11件EDA领域发明专利授权,40件实用新型专利授权和60多件软件著作权。

志存高远,敢啃最硬的骨头

芯和创业之初,就选了一块极其难啃的骨头——EDA软件。

EDA(Electronic design automation,电子设计自动化),是指利用计算机辅助设计(CAD)软件,来完成超大规模集成电路(VLSI)芯片的功能设计、综合、验证、物理设计(包括布局、布线、版图、设计规则检查等)、制造、封测的大型工业工具。

如今的集成电路,从系统架构开始,落实到功能的定义和实现,最终实现整个芯片的版图设计与验证,是一项复杂的系统工程,集成了人类智慧的最高成果。以华为2020年最新的7nm麒麟990芯片来说,其中集成了103亿颗晶体管,若没有EDA辅助,设计这样复杂的电路并保证良率是无法想象的。

简单地说,EDA就是芯片设计师的画笔和画板,就像操作文档要用Word,制作图片要用Photoshop一样,它能高效设计、控制及管理数十亿电路元件在一颗芯片里协同工作。

由此可见,EDA贯穿了集成电路产业链的每个环节,赋能了集成电路设计与制造的创新,是当之无愧的“芯片设计之母”。可以毫不夸张地说,没有站在产业链的顶端EDA,就不可能设计和制造当今的芯片。

“EDA软件不是简单用钱就能砸出来的行业。它融合了图形学、计算数学、微电子学、拓扑逻辑学、材料学及人工智能等多学科的算法技术,必须经过长时间技术积累和持续大规模研发投入,才能满足新工艺的应用需求。”代文亮介绍说。创业之初,他们凭借一股初生牛犊不怕虎的劲头,窝在一个小房间里搞研发,用了差不多4、5年的时间,把蕴藏在大脑中的想法通过算法变成一串串代码,然后又将一串串代码演变成一套套工程软件、本以为可以帮助企业实现芯片设计的部分国产替代。

然而,芯和的心血之作,一走向市场,就迎来了重要难题——EDA工具必须得到晶圆厂工艺节点的认证,设计公司才敢使用,否则因为设计差错带来的损失谁都承担不起;另一方面,晶圆厂对于EDA工具的评估和认证也是非常谨慎的,他们会优先选择EDA大厂,因为使用这些工具的设计公司众多,能够为晶圆厂的生产带来广泛的客源。而对于一些新进的EDA公司,由于客户数量有限,试错成本高,晶圆厂合作的兴趣不大。

逼上梁山,寻找破局之路

现实就是,国内大多数芯片设计公司都在采用进口的EDA工业软件来设计芯片,这就导致了国内芯片设计领域难以实现真正意义上的国产化。国产EDA软件几乎没有产业上下游使用的生态,这又造成进一步的恶性循环——本来代码还行,但是因为没有使用场景,得不到客户的反馈,就没有办法迭代,一旦没有迭代提升,代码很快就落后了。

怎么破局?

既然整体落后西方差不多20年,那就从局部突破。由于EDA工具覆盖面极广,从设计、生产到封测,涵盖了集成电路设计、布线、验证和仿真等所有流程。芯和选择了差异化工具,从仿真领域进行突破。“我本来就是研究仿真技术的,在我们看来,仿真代替测试是芯片设计领域的大势。”代文亮说,“尽管现在说起来轻松,但当初选择这么难的赛道,不少人都觉得我们是不是疯了。”

没有设计公司使用自己的软件,芯和就自己使用,然后根据自己的设计找晶圆厂生产、再找封装厂加工,并根据工厂的反馈不断迭代软件设计,就这样,“被逼”走上了芯片设计、生产与测试全链条的芯和,意外收获了足以支撑公司发展壮大下去的拳头产品——IPD滤波器。

代文亮进一步解释道,芯片工业发展到纳米级别,现实的物理世界已经很难去做实体验证。要想将实际开工后出现问题的概率降低,就必须利用仿真工具。“只要我们在仿真上做得比别人好,别人就会愿意切换工具使用我们的产品,从当初的点工具开始,我们做大厂不愿意去做的,或者反应比较慢的部分,渐渐进入EDA生态圈,和大佬们成为合作伙伴。”

目前,国产EDA公司中获得晶圆厂认证的不多,只有包括芯和半导体在内的少数几家。芯和半导体的生态圈建设经历十年建设,得益于在海外市场众多高科技企业用户的背书,目前已获得了晶圆厂主流工艺的众多认证。“获得认证也成为判断国产EDA公司是否成熟的一个标志。”

软硬兼备,打造滤波器龙头

敢于啃硬骨头的芯和,内部的IC设计团队就是芯和EDA工具上市前的第一个客户,经过他们实际项目验证的EDA工具发布后,无疑更能确保产品的效率和质量,就这样,芯和成为国内首批投资开发IPD技术的企业。

通过十几年的不断迭代更新,成功交付上百个产品和项目,芯和逐步确立起自己在中国无源器件(IPD)行业的龙头地位,并被全球著名的半导体分析机构Yole列入全球IPD滤波器设计的主要供应商之一。

目前在滤波器领域,94%以上的市场被国外厂商把控。作为国内少数几家拥有集成无源器件IPD技术的企业之一,随着5G的商用,芯和半导体IPD滤波器获得了市场的高度认可,成功进入了国内主流手机平台和射频芯片公司供应链,现在月平均出货量超过6000万颗,迅速占领了5G滤波器市场。截至2022年1月底,芯和半导体滤波器总出货量累积超过了10亿颗。

2022年6月,芯和又发布了最新的射频EDA/滤波器设计平台。其中包含EDA工具和滤波器设计两部分,覆盖了从射频芯片、封装、模组到板级的整个射频设计流程,更包含了IPD、Hybrid的滤波器技术和专为滤波器设计定制的EDA工具。

眼下,芯和联合国内领先工厂完成了工艺平台的开发,已完成多款IPD芯片的设计,并实现稳定量产供货。

代文亮感慨,十几年走来,芯和在IPD芯片及SiP模组的开发历程中,通过自身的勤奋与贴心服务,与众多国内外的晶圆厂及封装厂建立起了牢固的合作伙伴关系,并建立了通过晶圆验证的各类滤波器器件库。在目前半导体供应链异常吃紧的情况下,这个完善的生态圈将确保客户能够及时获所需的高质量滤波器产品。

从EDA仿真软件到滤波器,代文亮表示,芯和手握“一软一硬”两张王牌,也有利于缓解国内半导体产业的部分卡脖子问题。“美国对中国芯片行业的狙击,将会在未来一段时间显现。特别是先进制程的探索,芯和只是做了其中很小的一部分,需要更多的人投身EDA领域,才能把产业做大做强。”

再上层楼,从追随者迈向领跑者

尽管已经坐稳了国内IPD滤波器的头把交椅,芯和真正的杀手级应用实际上还是EDA。

早在2014年,芯和就开始布局Chiplet赛道。

Chiplet又称“小芯片”或“芯粒”,它是一种功能电路块。

通俗来讲,Chiplet技术就是将一个功能丰富且面积较大的芯片裸片(die)拆分成多个芯粒(chiplet),并将这些具有特定功能的芯粒通过先进封装的形式组合在一起,最终形成一个系统芯片。它是眼下半导体行业最热门的技术。

“用一个通俗的比喻,我们可以把半导体设计看作是建房子。之前的SoC技术是在平面上做文章,盖平房,现在是在三维上动脑筋,开始盖楼房了。”代文亮指出,与传统的SoC方案相比,Chiplet模式具有设计灵活性、成本低、上市周期短三方面优势。所以,将SoC拆分成几个关键的Chiplet可以更好地平衡研发成本,避免一颗大SoC芯片设计出来后没有足够出货量带来的巨大损失,从而缩短研发周期、研发人员投入等。

实际上,从AMD、亚马逊到Facebook、Google,全都在大力发展Chiplet技术。

因为起步早,再加上过往的行业积累,芯和再一次站在了浪潮之巅。

“国产替代,始终只是在以国外的某个产品、某项技术做对标。但是在日新月异的半导体行业,替代只能解决短期问题,你只能是一个追随者,永无出头之日。只有具备了宏大的国际化视野和超前的技术储备,运用创新思维去做事情,才有可能成为真正的强者。”代文亮说,“Chiplet虽然被认为是后摩尔时代延续芯片PPA的有效途径,但它作为一个新事物,倡导的是以系统设计为驱动,将设计、制造、封测工程师在一个协作平台上有效串联,这对传统的单芯片设计流程、设计工具甚至底层算法带来了巨大的颠覆。

“目前,EDA国际巨头都在齐头并进,希望尽快形成新的设计流程并形成客户粘性。芯和作为国内唯一一家已经在Chiplet先进封装领域进行布局的EDA公司,在2014年就发现了这个新的趋势,进行了积极的研发布局,并在2021年下半年全球首发了业界首款针对3DIC Chiplet先进封装的设计分析全流程EDA平台。”

芯和在仿真领域独树一帜的卓越能力和长期的精耕细作,让自己成为四大EDA——新思科技(Synopsys)、楷登电子(Cadence)、西门子(Siemens)和Ansys的全球官方合作伙伴,无缝嵌入到各大主流EDA设计平台中,并在用户易用性方面做了深层优化。

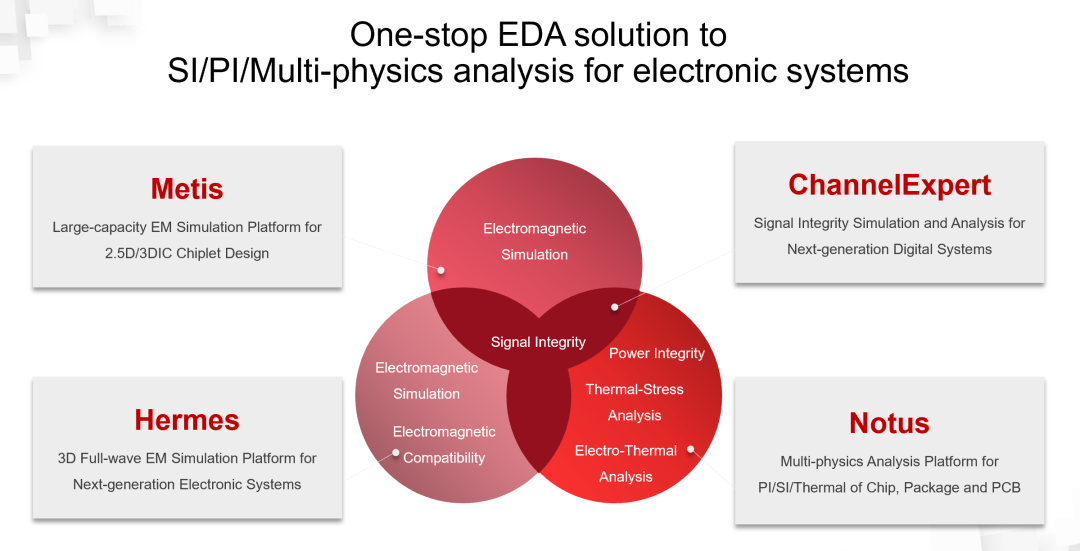

“他们拥有全流程的EDA产品,但我们的仿真EDA打通了后摩尔时代IC设计的所有仿真节点,全面支持先进工艺和先进封装。”代文亮自豪地说。

在先进工艺端,芯和半导体已经通过各大晶圆厂的主流工艺认证,具有业界顶尖的片上芯片建模和仿真能力,可保障芯片级的性能-功耗-尺寸(PPA)最佳平衡。去年,全球第二大晶圆厂三星宣布芯和半导体正式成为其SAFE-EDA生态系统合作伙伴,芯和的片上无源电磁场(EM)仿真套件已成功通过三星晶圆厂的8纳米低功耗(8LPP)工艺技术认证。

在先进封装端,芯和半导体的仿真分析方案从传统封装延伸到2.5D/3DIC异构集成封装领域,提供了完善的仿真分析能力。2021年,芯和与新思科技联合发布了全球首个3DIC先进封装设计分析EDA平台,开启了国内EDA与国际EDA强强联手的先河。

从2010年起步,芯和度过了无人喝彩的艰难创业期;如今,将全球总部放在上海的芯和,已受到上海各级政府和风投机构的热捧,一路高歌猛进,来到浪潮之巅。

代文亮对此深有感触,除了天使轮投资,公司之后获得的投资全部来自上海,特别是浦科创,对企业的发展给予了很大的帮助,从人才引进、科技立项、到业务对接,全方位帮助企业“赋能”,链接上下游相关企业,并在疫情期间,提供了包括房租减免在内的多项支持,为芯和的快速成长保驾护航。

中国人讲究十二年一个轮回。成立十二年后的芯和EDA,以Chiplet为旗帜,再一次开启新征程,助力集成电路进入中国“芯”时代。