引言

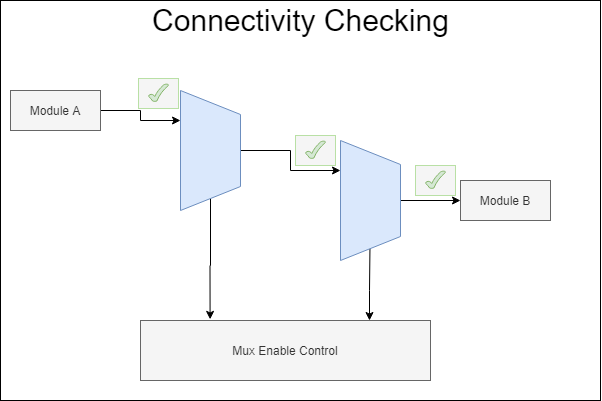

形式验证下的连接性检查是在芯片设计阶段进行的一种检查,旨在确保芯片的各个模块之间的连接是正确的、完整的,以及符合设计规范的。这种验证通常包括检查数据流、控制流和信号流,以验证芯片的各个部分是否能够正确地交互和协作,避免因连接错误导致的功能失效、性能下降或者其他问题。

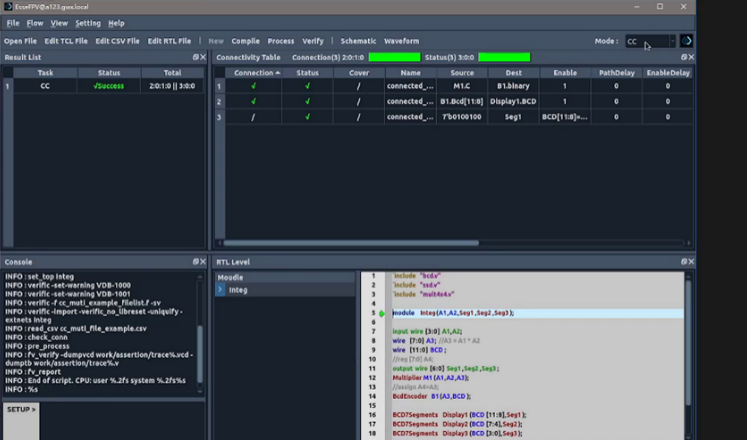

产品简介

EsseCC(Connectivity Checking,CC)主要用于检查芯片设计中端到端的物理连接、路径延迟等是否符合设计规范,以提供快速的错误检测和信号之间预期设计行为的验证。EsseCC以RTL电路和连接规范作为输入,详尽验证芯片内IP模块的静态、结构、时延等连接状态。与传统仿真验证方式不同,EsseCC具有高效、高准确率以及简单易用的优点,其强大功能包括反例生成、波形显示、原理图查看、源代码浏览和报告分析,能够为工程师节省大量调试时间。

▲ 测试模块与模块连接

应用场景

01SoC I/O 连接性检查

02综合后Netlist网表连接性检查

03验证chiplet技术下模块的连接性检查

04全局时钟及复位信号连接性检查

05总线寄存器的连接性检查

06集成IP的连接性检查

产品功能

01支持Verilog/System Verilog和VHDL的混合编译

02支持物理路径及连接属性的验证

03支持反向生成连接,自动生成高级连接规格

04支持连接信号的覆盖率检查

05支持生成反例的 testbench 及波形图

06支持所有连接类型,如常量、信号拼接、运算符、无延迟以及具有多个时钟和复位的流水线连接

07GUI界面提供原理图、波形查看

产品优势

01快速、高效的验证流程

02直观易操作的用户界面

▲GUI界面

03支持反例生成和波形显示

04支持多种引擎的连接性检查

05支持生成跨DFF的连接关系生成

06从已知的设计自动生成连接规格,用于生成设计的反向连接进行验证

07指定黑盒,节省验证时间

08自带debug功能,无需调用其他工具

09支持从RTL中提取连接,并验证随后的RTL修订中的任何意外更改

10完全自动化验证,工程师无需专门学习形式验证或SVA

EsseCC能够帮助设计人员快速、高效地发现设计中的问题,并提供直观易操作的GUI界面,使得验证与debug过程更加简单和直观。随着数字芯片设计的不断发展,EsseCC连接性检查工具将继续发挥着关键的作用,确保芯片设计的稳定性和可靠性,推动数字芯片技术的进步。