01课题背景

随着集成电路技术向超高密度方向发展,制造过程中对微小缺陷的容忍度大幅降低,产线的良率提升面临着巨大的挑战。然而,传统基于人工的缺陷检测方法效率低下并且强依赖于人工经验,难以满足集成电路产业对高精度和高效率的要求。现有的深度学习模型在处理复杂多变的晶圆表面缺陷时,仍然存在误检率高、无法识别新类型缺陷等难题,且无法实现对造成缺陷的原因进行自动化分析。由于产线相关的缺陷数据样本稀少、对缺陷数据的分析强依赖专家,以及对实时性和数据隐私的严格要求,使得自动化缺陷检测和根因分析在集成电路制造产线上的部署难度进一步加大。研究如何大幅提升缺陷检测的准确性并实现高效、准确的根因分析与知识问答,将成为虚拟制造发展的技术支撑,也是推动集成电路制造智能化升级的重要保障。

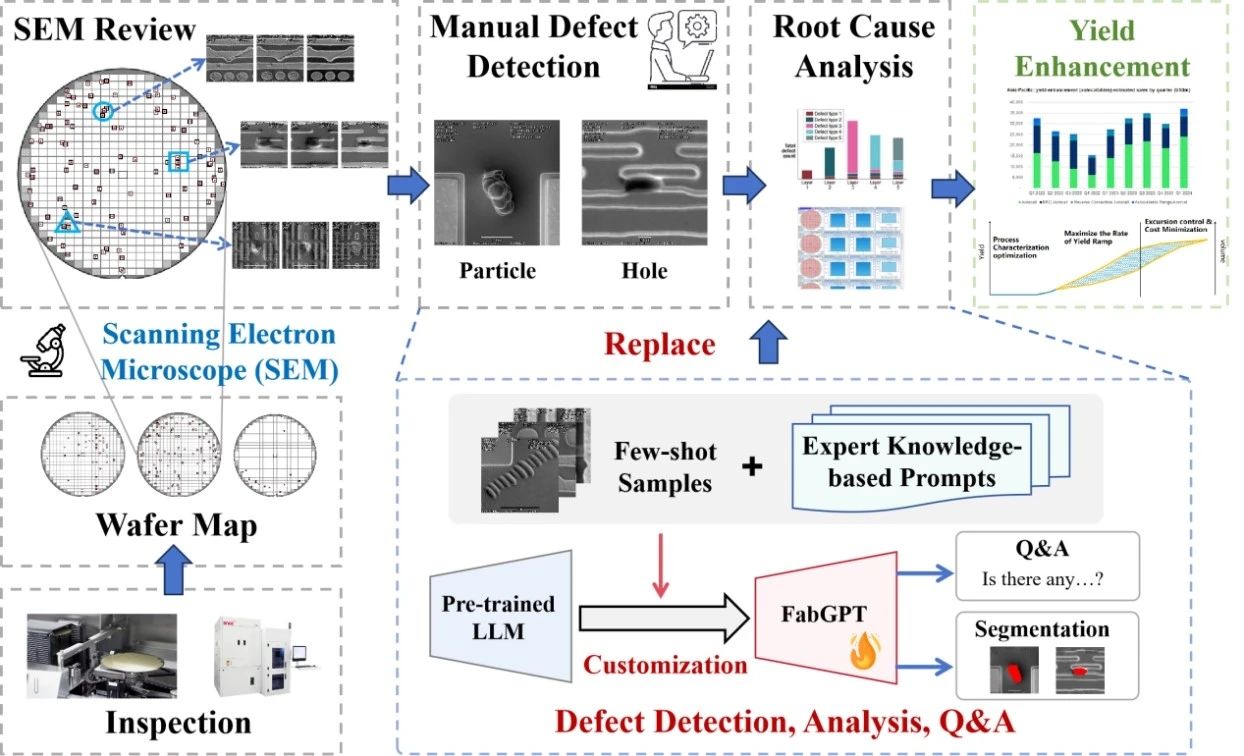

图1 FabGPT助力集成电路智能制造

02研究内容

近日,浙江大学集成电路学院卓成教授、孙奇研究员团队,提出了一种基于多模态的集成电路设计工艺协同优化大模型:FabGPT。该工作依托于吴汉明院士牵头的浙江省12吋CMOS成套工艺研发平台,通过少样本学习、多模态驱动的垂直领域知识学习和边缘加速器设计这三项核心技术,实现了精确的缺陷检测及根因分析、多模态IC领域交互问答和轻量化高效部署这三大核心功能。通过“产线-大模型-轻量化部署”协同设计,FabGPT直面行业痛点,着力实际生产力发展,为集成电路智造助力!该框架相关的三项工作均已发表于EDA领域国际顶级会议ICCAD 2024,第一完成人为浙江大学博士研究生金谦和姜钰琪、硕士研究生陈律丞。

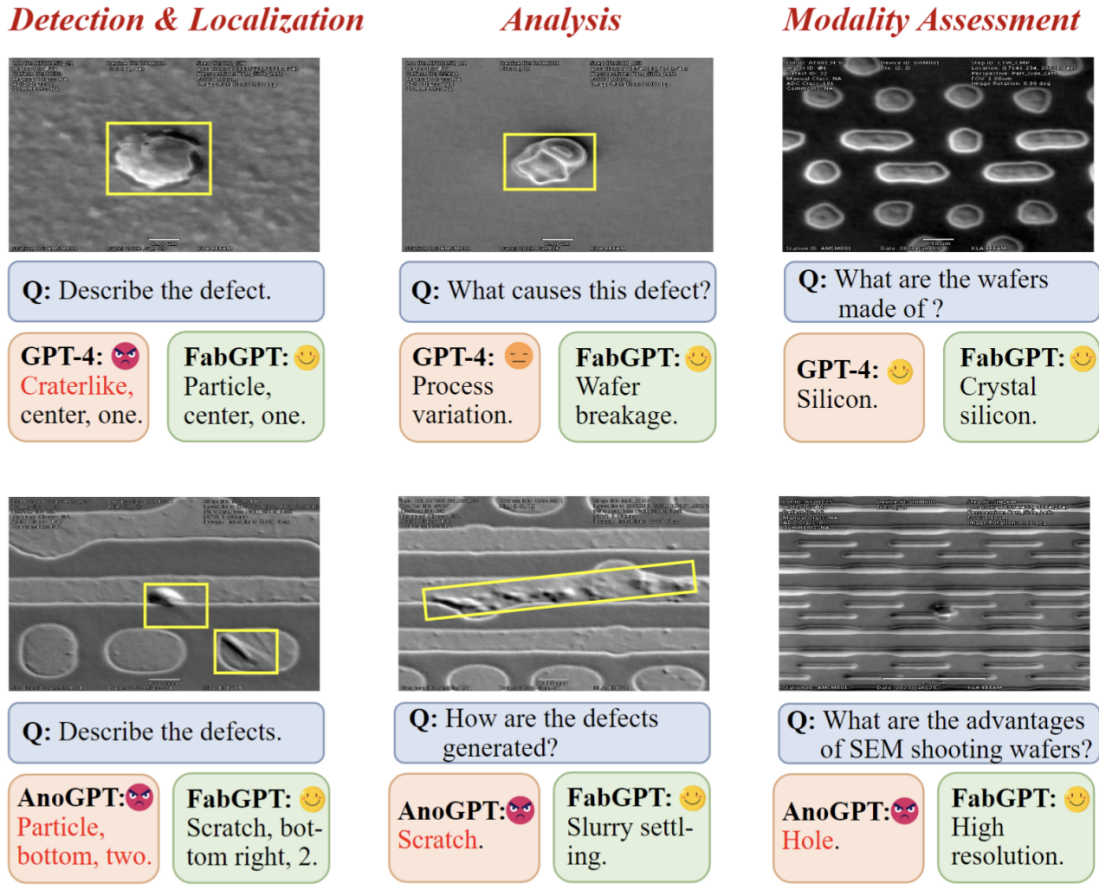

图2 FabGPT演示效果

03课题亮点

该工作面向集成电路虚拟制造需求,遵循少样本学习-知识推理-轻量化部署的技术思路,成功构建了大模型应用于集成电路智造的新范式。课题组通过有效迁移预训练模型中大量的先验知识,并引入双路径注意力机制来提取多层次的特征信息,减少了对产线数据的依赖,实现少样本下快速、准确的缺陷检测;利用Q-Former模块实现了晶圆缺陷图、诊断信息之间的多模态特征对齐,基于交互式语料库训练方法、IC专业知识和根因分析信息,完成对预训练大模型的垂直领域知识微调,同时缓解“模态偏差”问题,促使大模型能够正确完成相关缺陷图的根因分析和问答推理;最后,针对大模型推理时的计算瓶颈—矩阵/向量间乘法,设计了一个基于RISC-V的双核异构SoC系统,其包含专用于大模型的二值量化阵列加速器,同时支持二进制和浮点运算,具有完全可配置性和可扩展性,实现了高能效的FabGPT推理加速。

04前景展望

随着集成电路制造工艺的不断演进和超高密度集成技术的发展,FabGPT作为一种创新的集成电路设计工艺协同优化大模型,将在未来的制造领域发挥重要作用。通过引入少样本学习、多模态驱动的知识学习以及边缘加速器设计,FabGPT不仅能够在晶圆缺陷检测和根因分析中实现更高的精度和效率,还能在IC领域知识检索、问答方面展现出强大的能力。

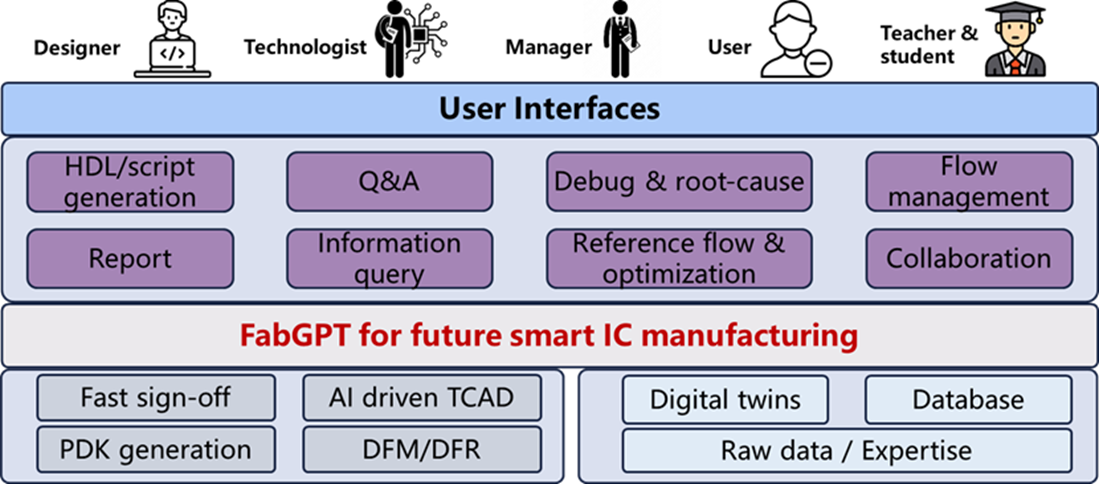

展望未来,研究团队将进一步优化FabGPT模型,拓展能力边界,使其能够支持HDL/脚本生成、代码调试、流程管理、知识检索、问答和制造流程优化等功能,提升其在集成电路制造各个环节中的应用价值,为设计、制造、管理、教学等提供全面的支撑。这一技术突破将为集成电路智造提供新的思路,推动半导体制造领域向智能化、自动化方向的快速发展,成为未来智能制造的关键支撑技术。

图3 FabGPT前景展望

评论

文明上网理性发言,请遵守新闻评论服务协议

登录参与评论

0/1000