中国射频EDA领军品牌法动EDA为解决用户需求,利用法动EDA电磁大脑人工智能技术加速法动FDSPICE®更优更快,为FDSPICE®赋能。

上一篇文章从理论创新的角度对法动FDSPICE®作了介绍,题为《法动EDA电磁大脑,创新中国本土FDSPICE®》;这一篇将从实战实用的角度介绍法动FDSPICE®。

法动FDSPICE®是一款功能强大的模拟/射频仿真工具,它能够对模拟/射频高速电路进行精确的仿真和分析。通过仿真电路在各种条件下的行为,设计师可以更好地理解电路的性能,并对其进行优化。这种仿真能力使得FDSPICE® 成为模拟/射频高速电路设计领域的一款重要工具。

法动FDSPICE®提供了丰富的模型和库文件,这些模型涵盖了各种模拟/射频元件和电路结构。设计师可以利用这些模型和库文件快速搭建和仿真复杂的模拟/射频电路,大大提高了设计效率。同时,这些模型和库文件都是经过严格验证的,确保了仿真结果的准确性和可靠性。

法动FDSPICE®还具有强大的优化功能。它可以根据设计师设定的目标和约束条件,自动调整电路参数以达到最优性能。这种优化功能够大大简化设计过程,提高设计的成功率。同时,FDSPICE® 还提供了丰富的优化算法和策略,设计师可以根据自己的需求选择合适的优化方法。

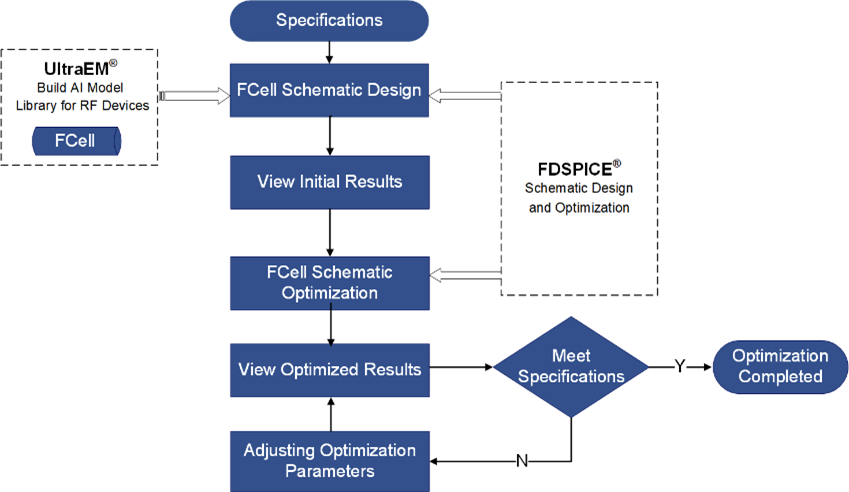

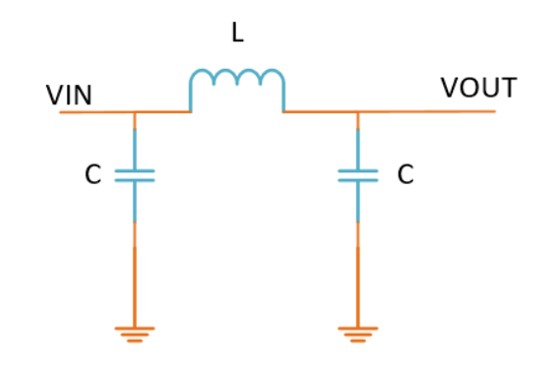

以下,从一个LC滤波器为例,介绍法动FDSPICE®的优化流程,操作流程如下图1。

图1 优化流程图

01制定规格

图2 LC滤波器电路图

设计指标:

02在UltraEM训练AI库单元(FCell)

AI库单元通常由FCell定义,UltraEM®可以用来构建FCell。

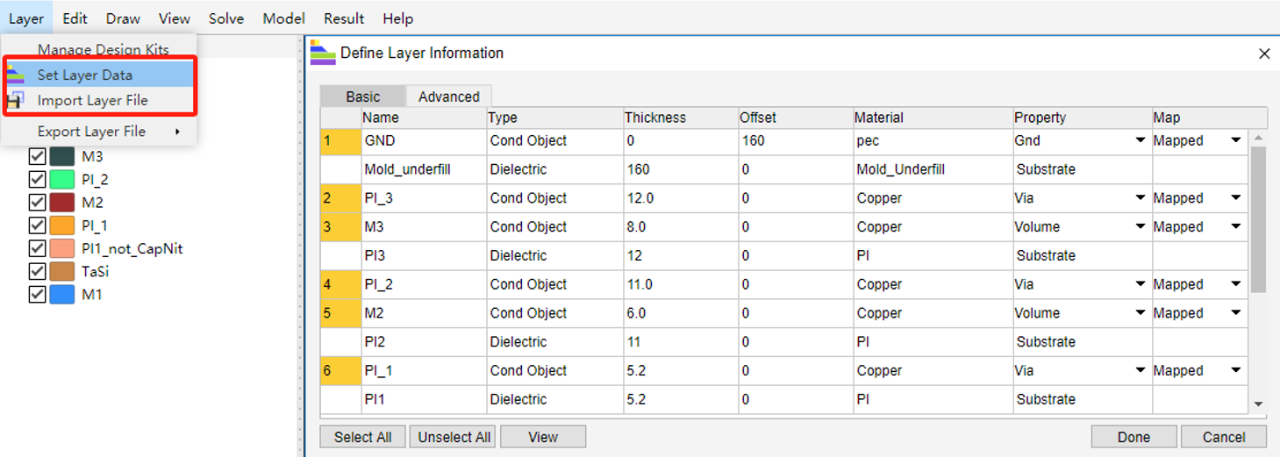

1.设置工艺。在UltraEM®中用户可以导入工艺文件,也可以手动设置如图3所示。

图3 设置工艺

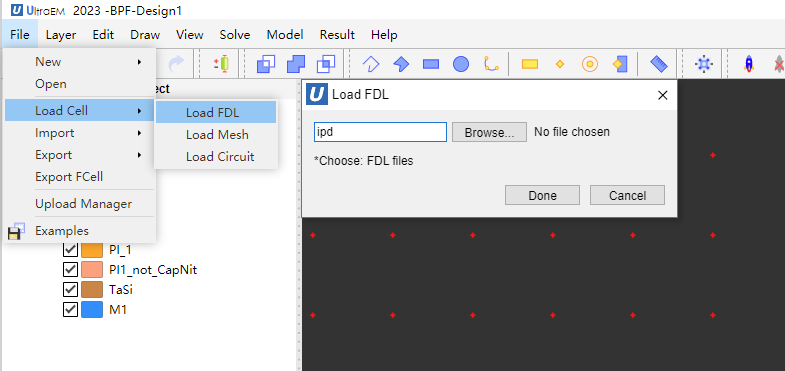

2.编写并导入库文件。用户需要使用Python语言编写库单元文件,导入UltraEM®的库中,如图4所示。

图4 导入库文件

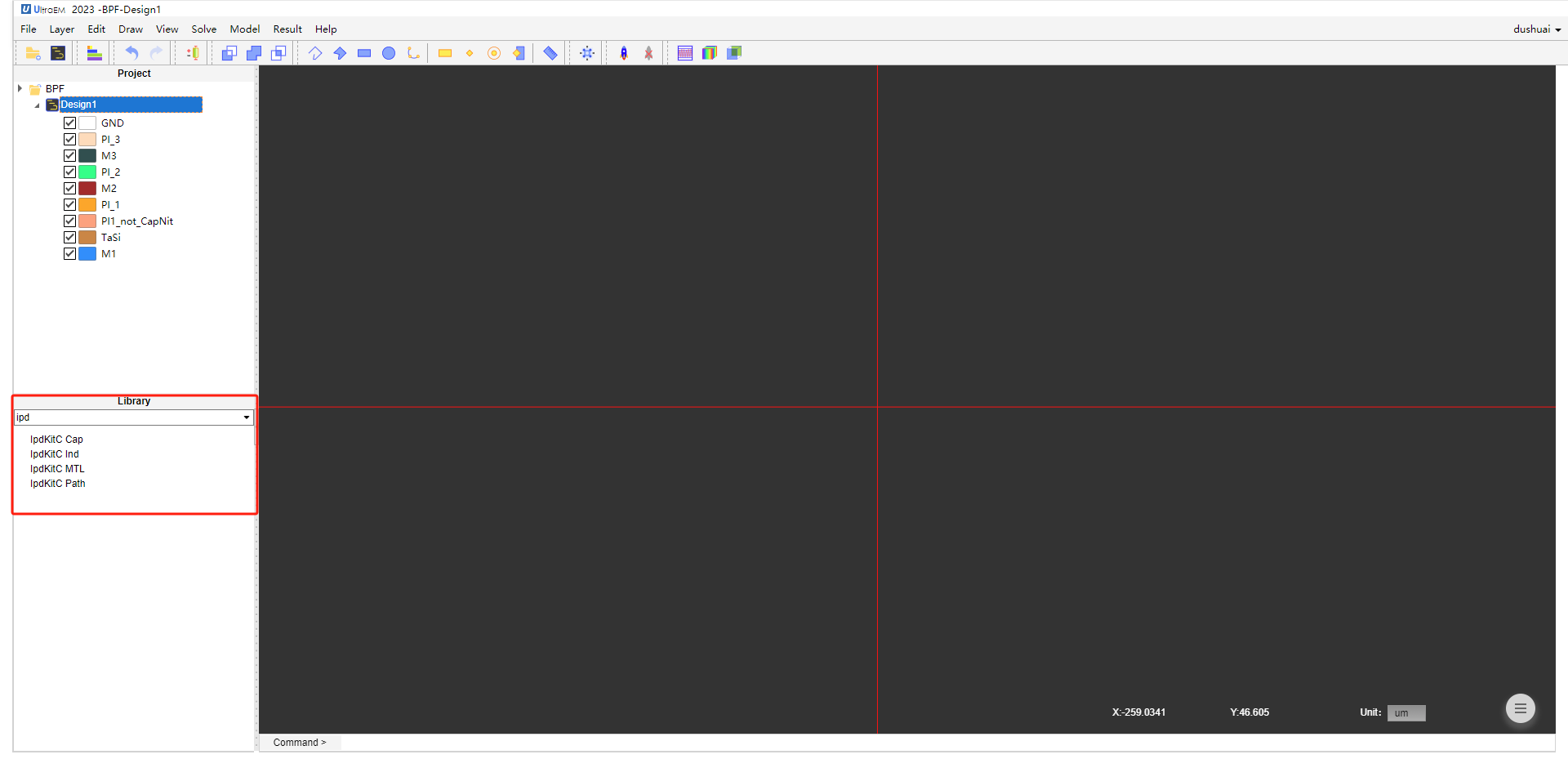

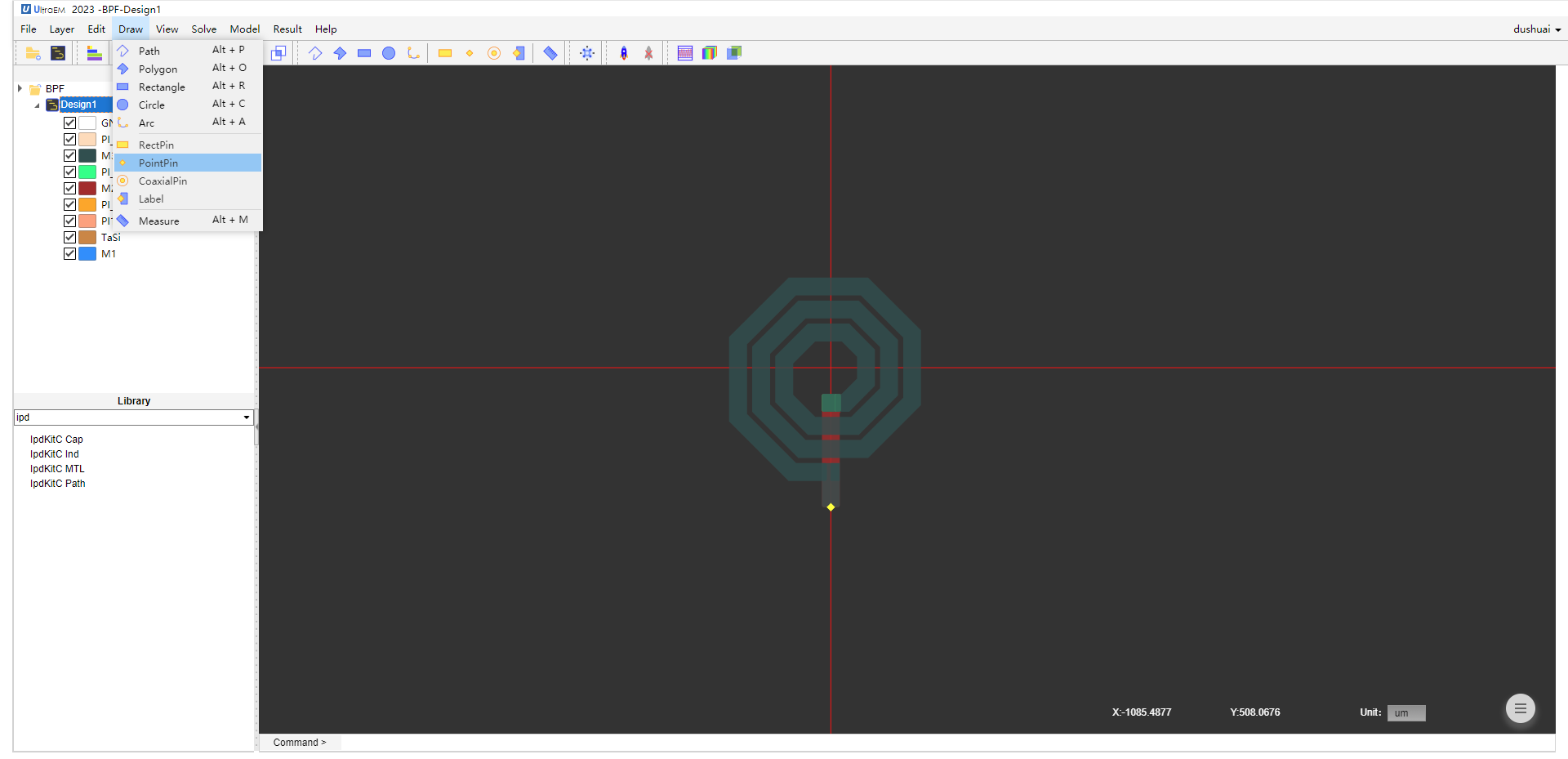

库单元导入后可在用户界面左下角Library界面调用,如图5所示。

图5 调用库文件

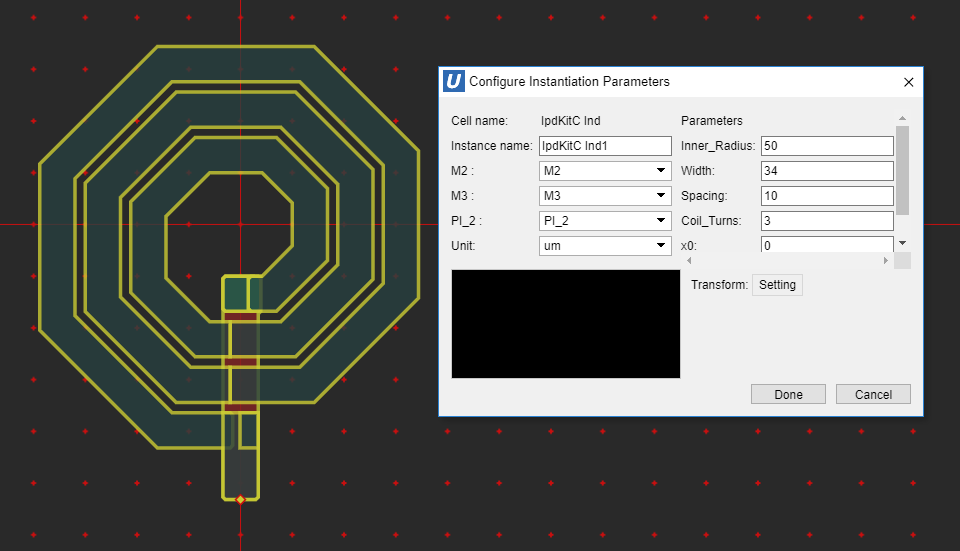

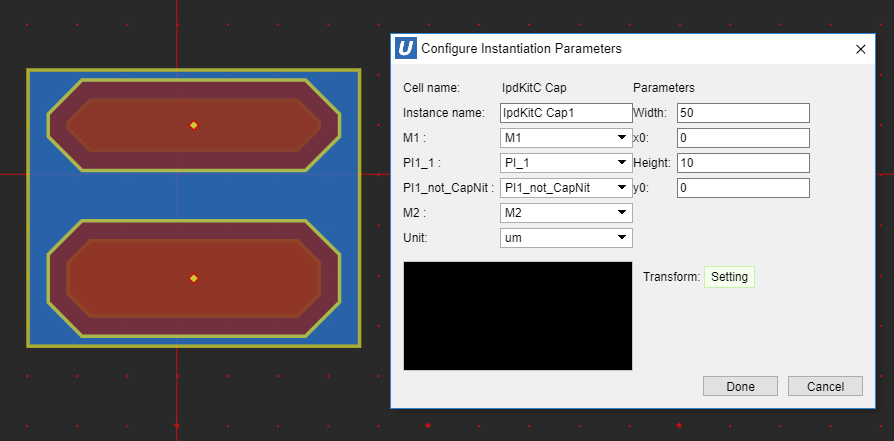

3.AI训练。调用库单元如图6、图7所示。

图6 UltraEM®中的参数化电感模型

图7 UltraEM®中的参数化电容模型

添加激励,如图8所示。

图8 添加激励

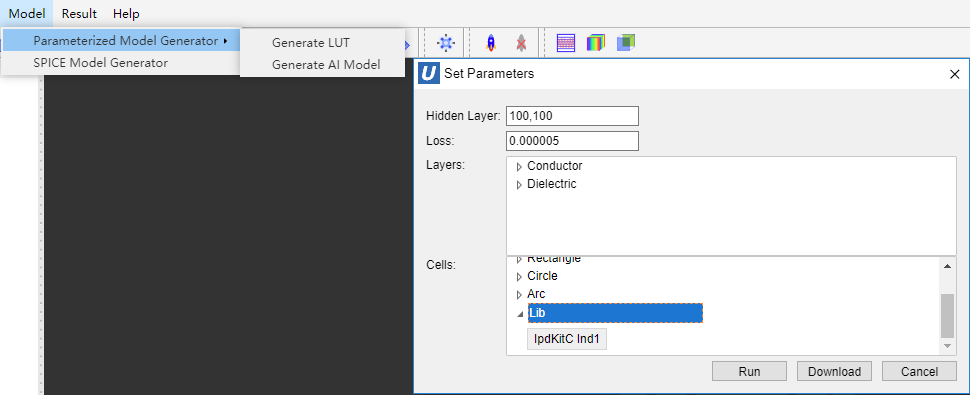

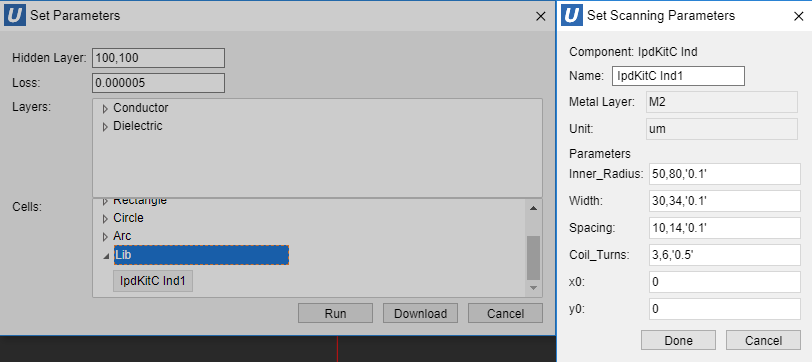

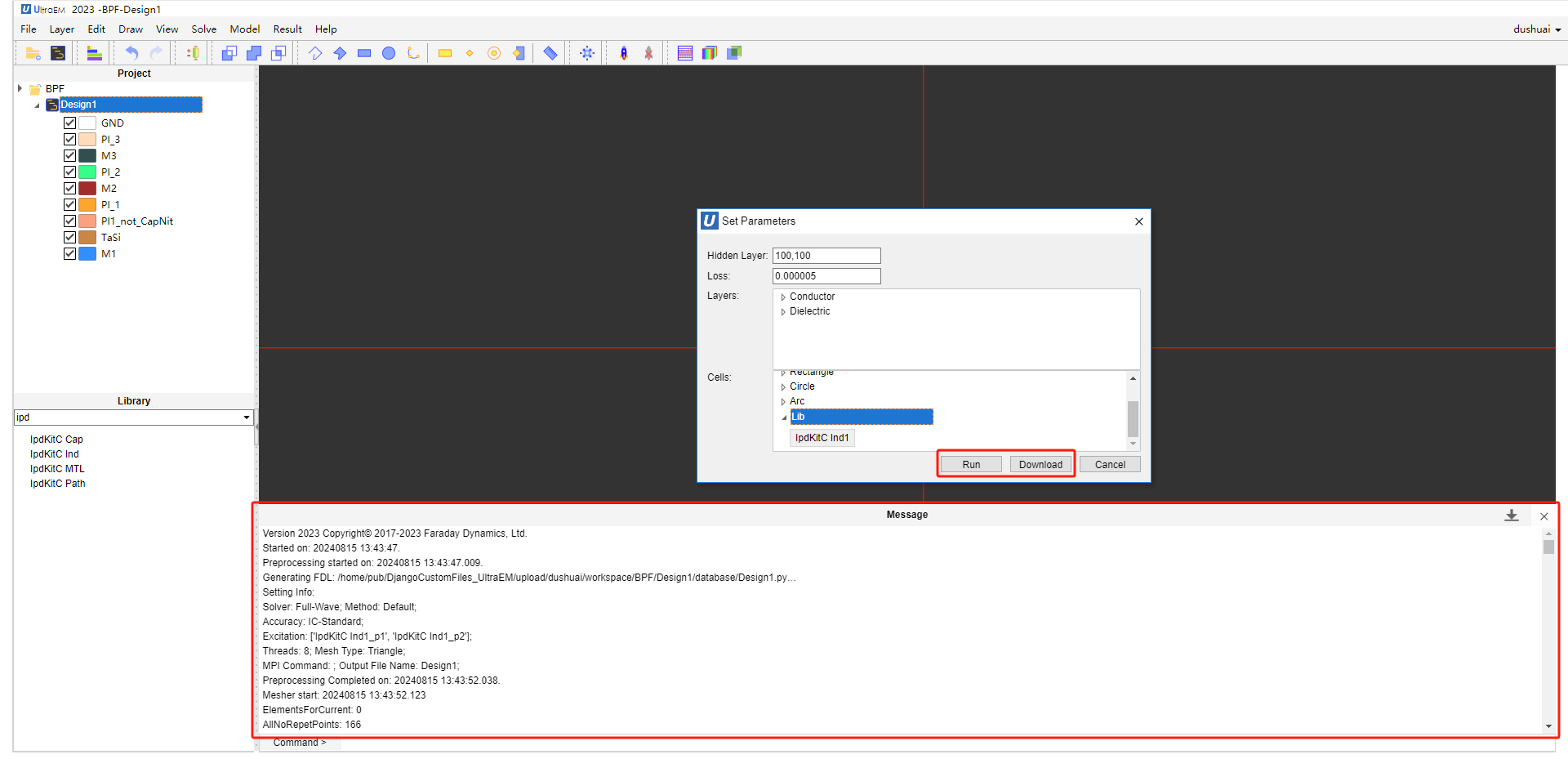

进行AI训练参数范围设置(参数范围用“,”相隔),如图9、图10所示。

图9 AI训练

图10 参数范围设置

下载FCell。点击Run,在Message栏中显示完成训练后,点击Download,下载FCell供FDSPICE®和其他法动软件工具使用,如图11所示。

图11 完成AI训练

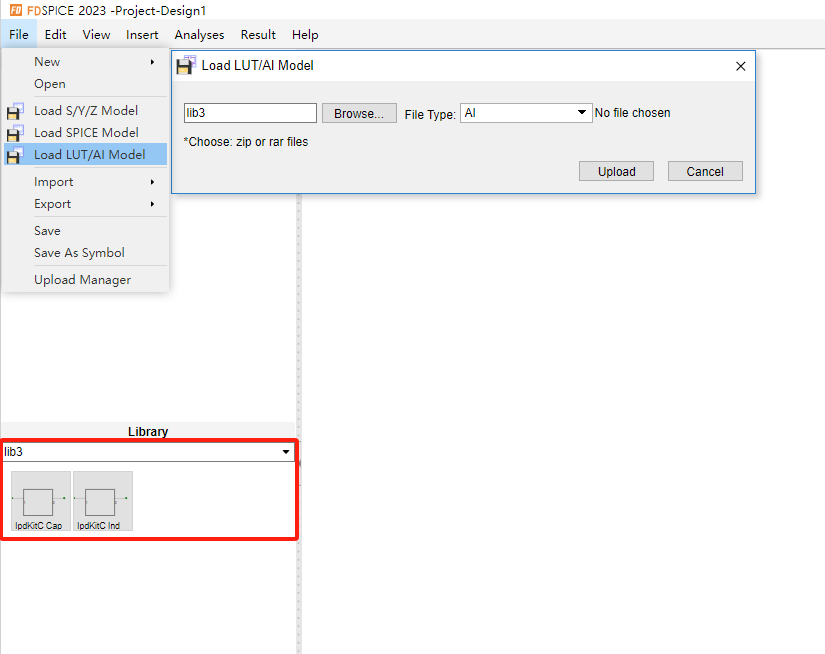

03导入FCell

用户需要在FDSPICE®导入AI训练得到的FCell,导入后如图12所示。

图12 导入AI Model

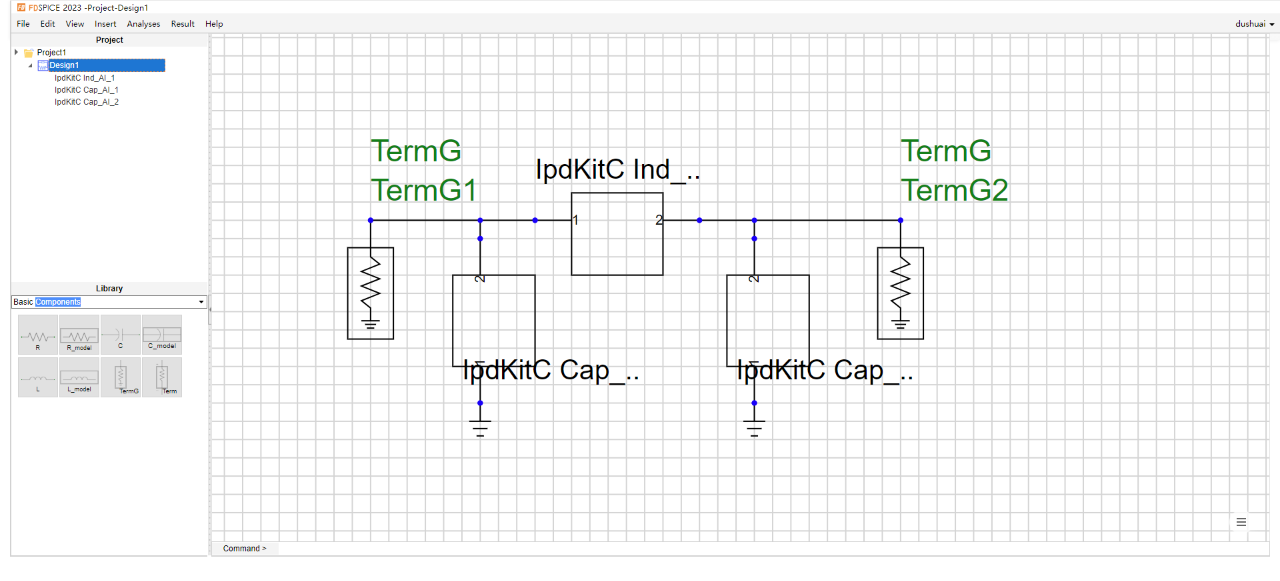

04连接电路并查看结果

在FDSPICE®放置FCell并连接电路图,添加激励后如图13所示。

图13 添加激励

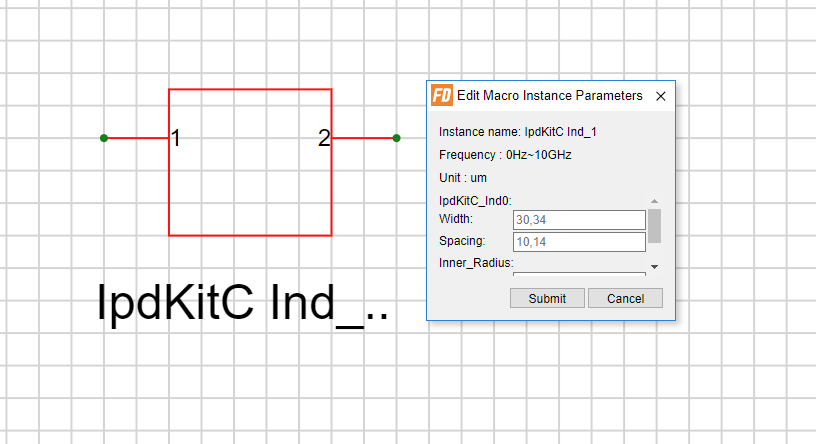

双击导入的FCell设置参数,如图14所示。

图14 参数设置

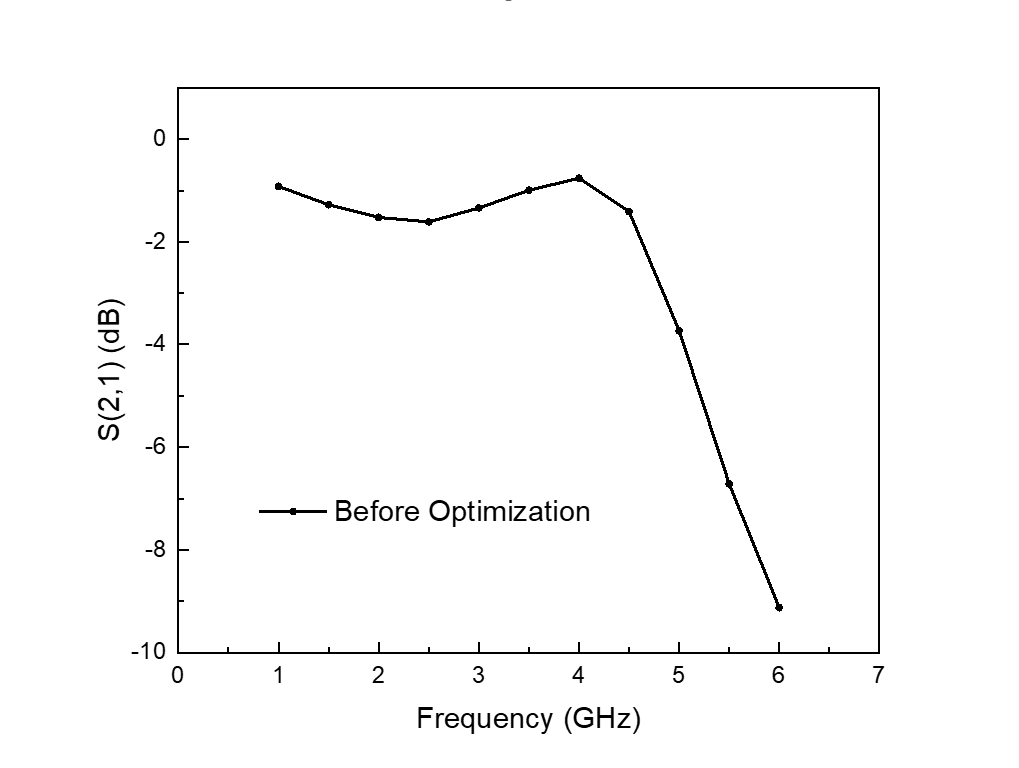

初步仿真结果如图15所示。

图15 初步仿真结果

当前结果在通带1-3GHz的插损为1.6dB,大于1dB,不符合设计指标。

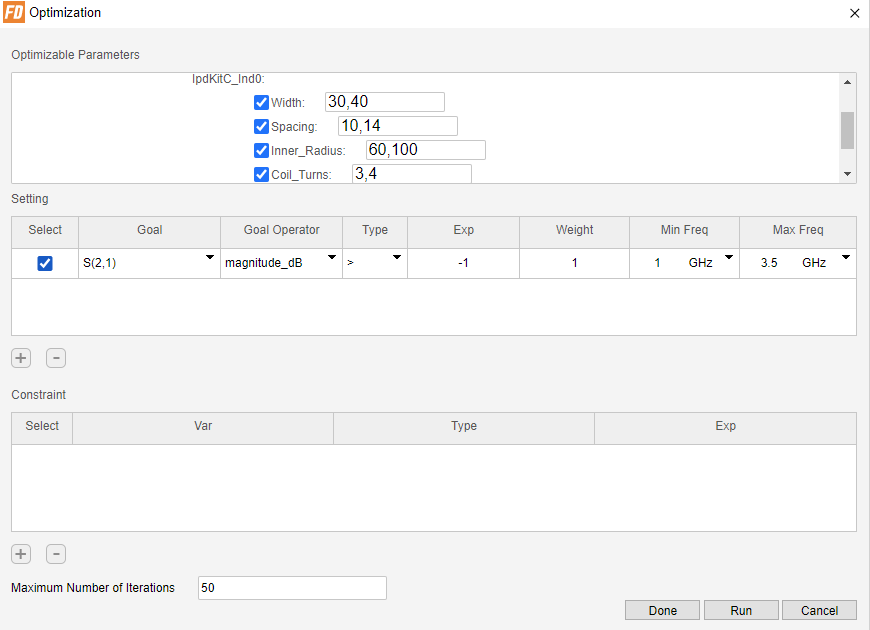

05设置优化目标及参数范围

使用Optimization功能优化电路,设置优化目标及参数范围,如图16所示,设置的电感内径参数范围为50-100um,设置优化目标插损在1-3.5GHz时小于1dB。

图16 设置优化目标及参数范围

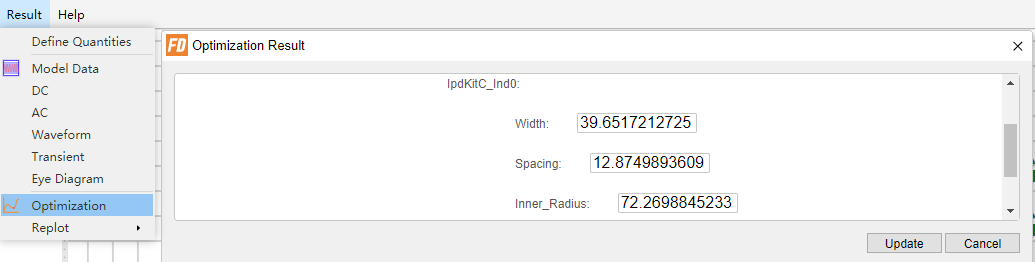

优化结果如图17所示。

图17 优化结果

06查看结果

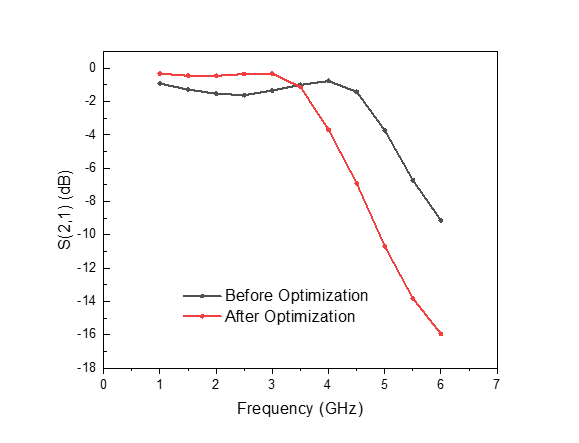

应用参数后再次仿真,结果如图18所示,在1-3.5GHz,插损小于1dB,达到期望指标,优化完成。

图18 优化前后结果对比

以上,基于一个LC滤波器为例对FDSPICE®的设计优化流程进行了详细介绍,直观地展示了FDSPICE®的优化功能在实际设计中的应用。首先,设定了通带、插入损耗和截止频率等设计指标;然后,在UltraEM®中对LC滤波器的电路单元L和C分别通过设置工艺、编写并导入Python几何描述文件、添加激励、扫描等步骤完成FCell建库;将FCell单元库导入FDSPICE®并完成LC滤波器的初步设计;在初步仿真结果不符合设计指标的情况下,利用FDSPICE®的优化功能对电路进行了优化,通过设定优化目标和参数范围,FDSPICE®成功地找到了满足设计要求的最佳参数组合。最终,优化后的LC滤波器在通带范围内的插损达到了设计要求,验证了FDSPICE®优化功能的有效性。此外,FDSPICE®可以处理包含有源器件的仿真及优化,也可以处理原理图和版图的联合仿真及优化。

综上所述,FDSPICE® 作为一款用于模拟/射频高速电路设计优化的EDA工具,具有功能强大、模型丰富、优化能力强和界面友好等优点。它能够帮助设计师更好地理解和优化模拟/射频高速电路,提高设计效率和质量。