研究内容

近日,浙江大学集成电路学院张亦舒团队提出了基于氧化钨制备的CMOS工艺兼容的高性能自整流忆阻器。该工作以题为“High-performance CMOS-compatible self-rectifying memristor for passive array integration”发表于Physical Review Applied。本文第一作者为浙江大学集成电路学院博士生王字健。该工作得到了国家自然科学基金委员会和浙江省自然科学基金重大项目的资助。

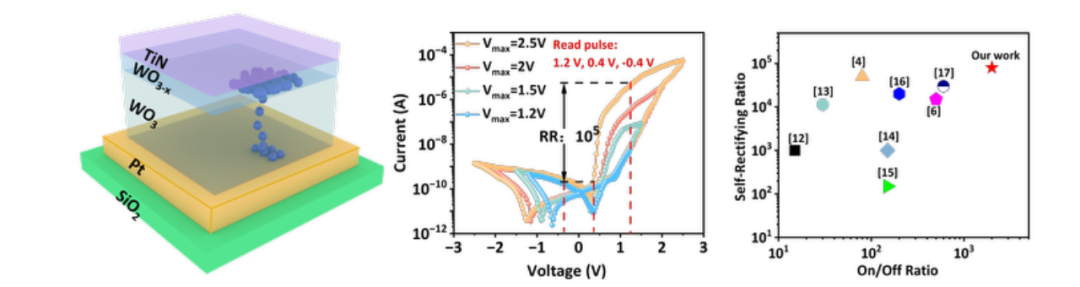

本研究团队选用了钨的氧化物WO₃作为核心材料。钨是CMOS工艺中常用的金属互连材料,这使得整个器件具有与现有工艺高度兼容的优势。器件采用简单的单氧化层结构,简化了制备工艺,并有效降低了工业成本。

图 论文部分成果展示

在性能方面,该器件展示了约103的开关比和105的整流比,表现出出色的稳定性,可在室温下保持106秒以上的数据保持能力和104次循环以上的循环寿命。在100×100的阵列集成中,器件实现了97.3%的电阻读取精度。当读取裕度设置为10%时,基于该器件的无源阵列可以达到180.3 Gb的存储容量。研究团队还基于32×32的无源阵列模拟了片上卷积神经网络,在手写数字“0”、“1”和“2”的识别任务中取得了99.1%的识别准确率。

这项研究不仅在材料和工艺上实现了创新,更为自整流忆阻器在标准CMOS制造工艺中的集成提供了可行方案。该成果为突破存储器件密度限制和推动神经形态计算的发展开辟了新的途径,为大规模存储和类脑计算应用提供了重要的技术支撑,展示了在后摩尔时代推进集成电路技术发展的巨大潜力。

研究背景

随着后摩尔时代的到来,集成电路的发展面临着传统架构的瓶颈,如何突破存储器件的密度限制成为关键。忆阻器作为新一代的非易失性存储器件,因其高密度集成和类脑计算潜力而备受关注。然而,传统的忆阻器在高密度阵列集成中会产生严重的串扰效应,影响器件的读取准确性,与CMOS工艺不兼容的材料体系也制约了其实际应用。

自整流忆阻器的出现为这一问题提供了有效的解决方案。自整流忆阻器在正向电压下导通,负向电压下截止,能够有效抑制反向电流,从而当集成于被动阵列时避免了读取高阻态器件时周边低阻态器件导致的渗透电流。这种特性使得无需额外的选择器件,就能实现高密度的无源交叉阵列,降低了制造成本和复杂度。

研究团队简介

张亦舒 浙江大学杭州国际科创中心百人计划研究员、求是科创学者,浙江省海外高层次人才

长期从事围绕新型存储器(RRAM, FeRAM等)实现的存算一体和神经形态计算研究,在相关领域发表学术论文50余篇,其中第一作者/通讯作者论文25篇,包括《Nature Communications》、《Advanced Materials》(4篇)、《Advanced Functional Materials》、《InfoMat》和《Nano Letters》(5篇)等;以第一发明人申请发明专利16项,授权6项,其中2项美国专利。参与编著由吴汉明院士主编的《集成电路制造大生产工艺技术》教材第17章。主持参与包括国家自然科学基金,科技部重点研发计划,浙江省重大基金在内的多项省部级项目。受邀担任International Journal of Extreme Manufacturing、Brain-X、Progress in Natural Science-Materials International和CMC-Computers Materials & Continua等国际学术期刊青年编委。获得包括第二届全国博士后创新创业银奖和国家优秀自费留学生奖学金等奖项。

王字健 浙江大学集成电路学院2022级直博士

曾前往加拿大滑铁卢大学交流,从事自整流RRAM器件的集成,光感存算一体化以及新型神经形态器件方面的研究。目前已经在《Physical Review Applied》《International Journal of Extreme Manufacturing》《Applied Physics Letters》《ACS Applied Materials & Interfaces》《Advanced Material》等期刊发表SCI论文七篇,其中第一作者论文2篇。中国发明专利两项。