1.展讯通信“通信指示方法及相关产品”专利公布

2.奕斯伟“硅片抛光方法和硅片抛光设备”专利公布

3.左蓝微“一种声表面波谐振器质量负载制备工艺及半导体结构”专利公布

4.智芯微“多芯片三维封装结构及封装方法”专利公布

5.速腾聚创“一种激光雷达的接收控制方法、装置以及激光雷达”专利公布

1.展讯通信“通信指示方法及相关产品”专利公布

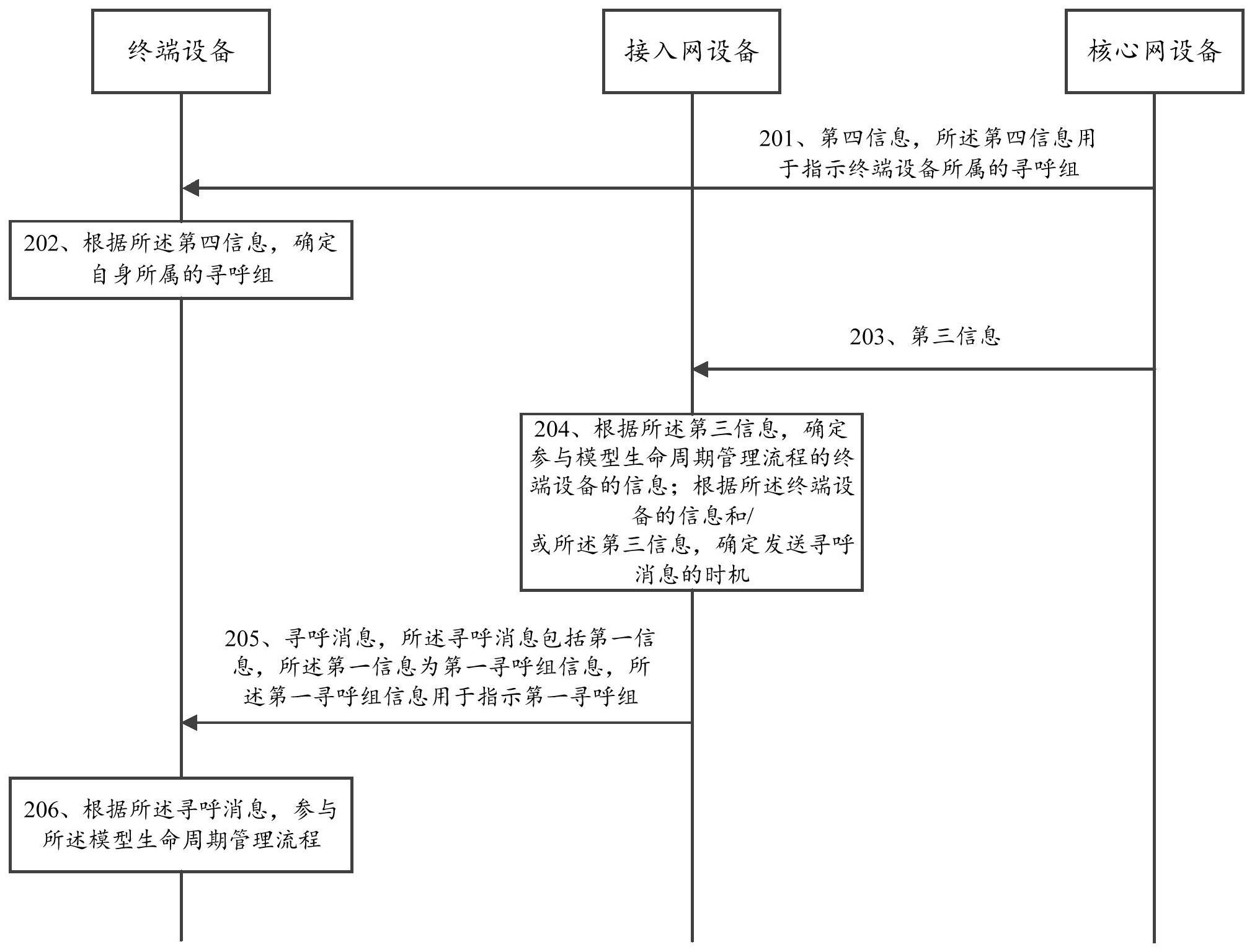

天眼查显示,展讯通信(上海)有限公司“通信指示方法及相关产品”专利公布,申请公布日为2025年2月28日,申请公布号为CN119545519A。

本申请实施例公开了一种通信指示方法及相关产品,所述方法包括:发送寻呼消息,所述寻呼消息包括第一信息,所述第一信息用于指示参与模型生命周期管理流程的终端设备,所述终端设备处于无线资源控制非连接态。采用本发明,能够有效指示处于非连接态的终端设备参与模型生命周期管理流程。

2.奕斯伟“硅片抛光方法和硅片抛光设备”专利公布

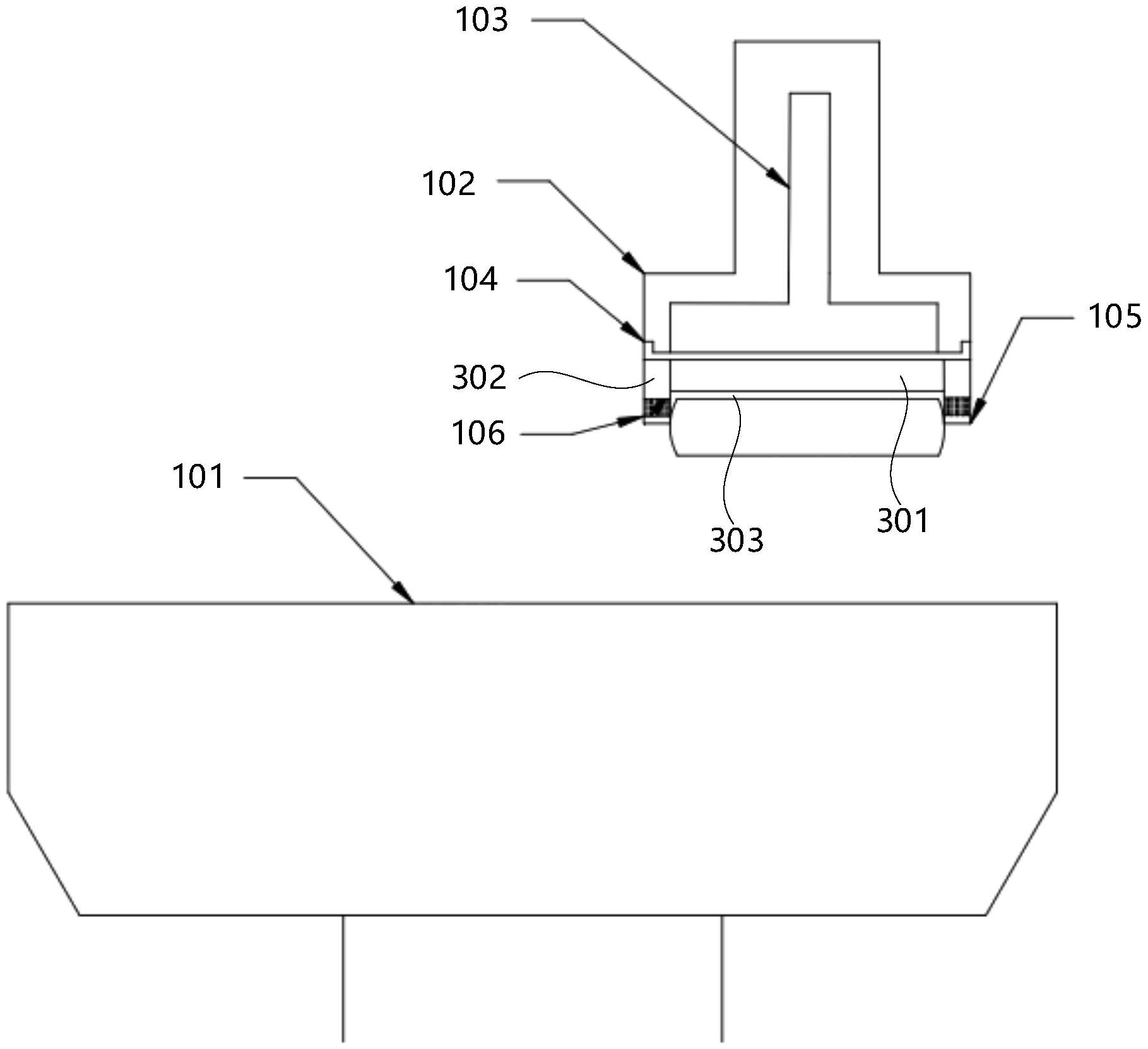

天眼查显示,西安奕斯伟材料科技股份有限公司“硅片抛光方法和硅片抛光设备”专利公布,申请公布日为2025年2月28日,申请公布号为CN119526238A。

本申请提供了硅片抛光方法和硅片抛光设备,硅片抛光设备的模板组件包括薄膜基部和环部,所述环部自所述薄膜基部的边缘延伸以形成用于保持硅片的凹槽,所述环部设置有伸缩单元,所述方法包括:在所述硅片的抛光过程中,检测所述环部的磨损应力,以得到应力数据;在所述应力数据未处于目标数值范围内的情况下,调整所述伸缩单元的长度,以改变所述凹槽的深度。本申请通过监测环部的磨损应力并自动调整伸缩单元的长度,实现了TA尺寸的自动调节,提高了设备的自动化水平和稼动率,能够有效减少TA因磨损应力过大而导致的过度磨损,延长了TA的使用寿命。此外,自动调控TA尺寸,能够保障硅片边缘的去除量在合理水平,提升硅片的边缘平整度和产品质量。

3.左蓝微“一种声表面波谐振器质量负载制备工艺及半导体结构”专利公布

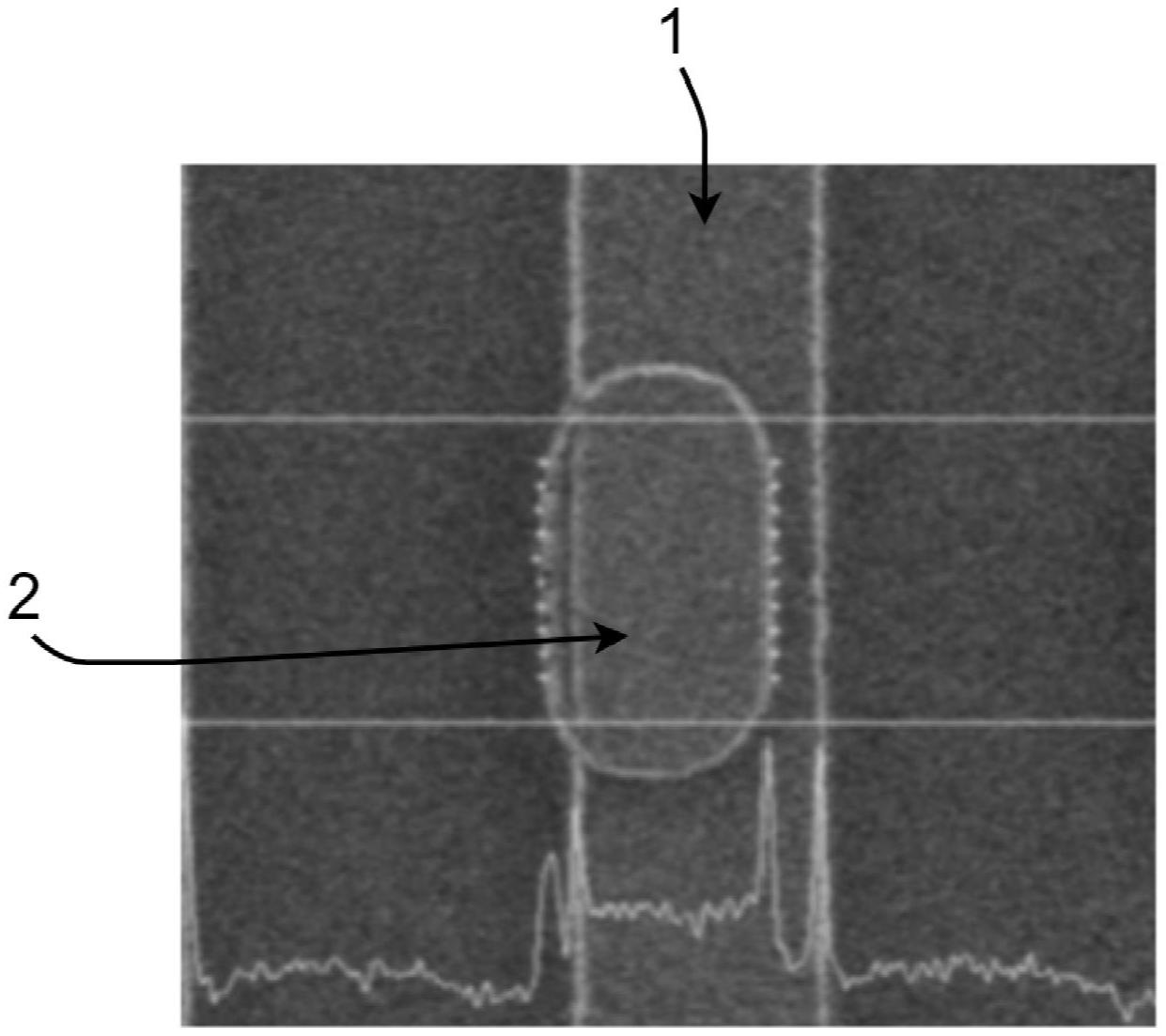

天眼查显示,左蓝微(江苏)电子技术有限公司“一种声表面波谐振器质量负载制备工艺及半导体结构”专利公布,申请公布日为2025年2月28日,申请公布号为CN119543860A。

本发明公开了一种声表面波谐振器质量负载制备工艺及半导体结构,该制备工艺包括:准备晶圆;利用光刻工艺在晶圆上形成第一光刻胶图层;在形成有第一光刻胶图层的晶圆上按照设计厚度要求沉积一层IDT材料的薄膜;在完成IDT镀膜后的晶圆上形成第二光刻胶图层;在形成有第二光刻胶图层的晶圆上按照设计厚度要求沉积一层质量负载材料的薄膜;最后剥离晶圆上的光刻胶,使得覆盖于光刻胶上的IDT材料薄膜和/或质量负载材料薄膜一同被剥离,未覆盖于光刻胶上的IDT材料薄膜和质量负载材料薄膜则被保留。采用该工艺大大降低了对套刻精度的要求,能更好的控制产品的一致性、提高产品质量。

4.智芯微“多芯片三维封装结构及封装方法”专利公布

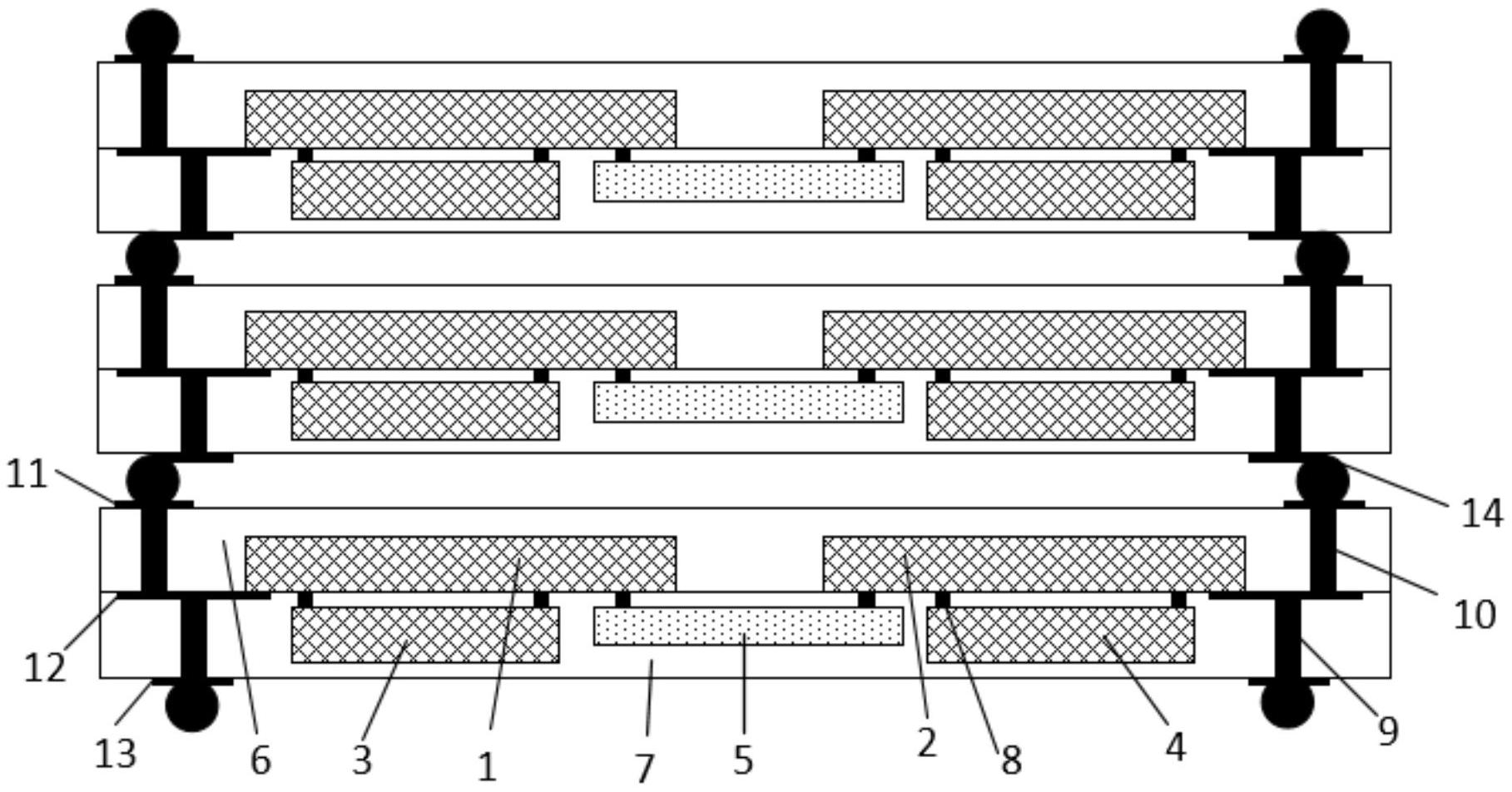

天眼查显示,北京智芯微电子科技有限公司“多芯片三维封装结构及封装方法”专利公布,申请公布日为2025年2月28日,申请公布号为CN119545887A。

本发明涉及芯片封装技术领域,提供一种多芯片三维封装结构及封装方法。所述封装结构包括:多个模塑介质层以及多个芯片组,多个芯片组分别塑封于多个模塑介质层中,多个芯片组通过模塑介质层中的塑封通孔实现互连;相邻两个芯片组的多个芯片倒装于相邻两个模塑介质层之间的再布线层上;相邻两个芯片组中至少一个芯片组包括多个具有高速率接口和低速率接口的芯片,该芯片组的多个芯片的高速率接口通过互连桥连接,相邻两个芯片组中各芯片的低速率接口通过相邻两个模塑介质层之间的再布线层引出至塑封通孔。本发明采用互连桥并使用塑封通孔(TMV)与再布线层(RDL)相结合的封装工艺,降低了多芯片三维封装的技术难度和制造成本。

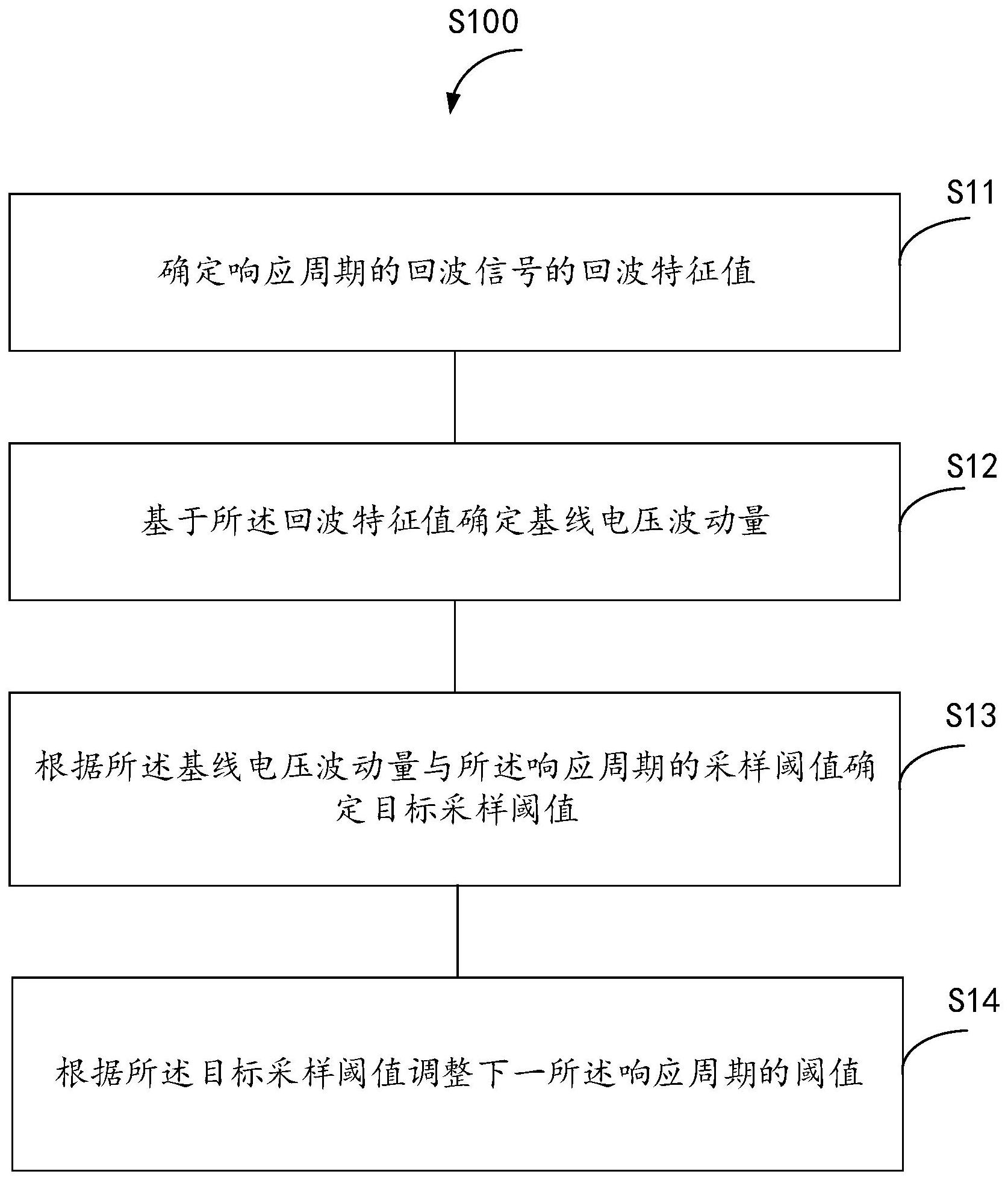

5.速腾聚创“一种激光雷达的接收控制方法、装置以及激光雷达”专利公布

天眼查显示,深圳市速腾聚创科技有限公司“一种激光雷达的接收控制方法、装置以及激光雷达”专利公布,申请公布日为2025年2月28日,申请公布号为CN119535414A。

本发明实施例公开了一种激光雷达的接收控制方法、装置以及激光雷达,该方法首先确定响应周期的回波信号的回波特征值,然后基于回波特征值确定基线电压波动量,再根据基线电压波动量与响应周期的采样阈值确定目标采样阈值,最后根据目标采样阈值调整下一响应周期的阈值。该接收控制方法对采样阈值进行补偿,得到补偿后的目标采样阈值,实现回波信号的准确采样,提高测距效果,同时,相对于固定阈值补偿,该接收控制方法基于接收到的回波信号对基线电压的影响,实时调整采样阈值,使得调整后的采样阈值与基线电压的波动趋势一致,使得目标采样阈值与回波信号更加匹配,进一步提高采样精确度。

评论

文明上网理性发言,请遵守新闻评论服务协议

登录参与评论

0/1000