3月25日-27日,备受业界瞩目的半导体行业盛会SEMICON China 2026在上海新国际博览中心盛大举行。在展会首日,长电科技董事、首席执行长郑力发表题为《先进封装的原子级革新定义芯片成品制造新范式》的主题演讲,围绕后摩尔时代芯片制造路径演进,系统阐述了先进封装从“辅助角色”走向“核心驱动力”的关键转折,并指出原子级精度正成为推动产业变革的重要引擎。

郑力表示,随着集成电路持续向更先进节点演进,传统依赖晶体管微缩的路径正逐步逼近物理极限,行业亟须新的技术范式来承接算力增长需求,而先进封装正是在这一背景下迎来历史性机遇。

从微缩逼近极限到系统级重构,先进封装成制造新主线

郑力指出,先进逻辑制程正逼近更严峻的物理与经济约束,单纯依赖传统微缩路径提升系统性能的难度显著增加。 在这一背景下,混合键合等先进封装技术的发展,使芯片成品制造真正走上了系统化集成之路。

“过去我们一直强调微缩,但当物理极限逐渐显现时,必须寻找新的路径。”郑力表示,早在摩尔定律提出之初,市场就已经提出系统集成的思路,而在当前阶段,这一路径正在从理论走向现实。

他进一步指出,过去几年虽然行业持续关注先进封装,但受限于精度与工艺能力,其尚未真正承担核心角色。而随着关键技术突破,先进封装正在迎来“转折点”,开始从配套环节走向产业主线。

原子级精度驱动制造范式跃迁,芯片性能迈向系统级新高度

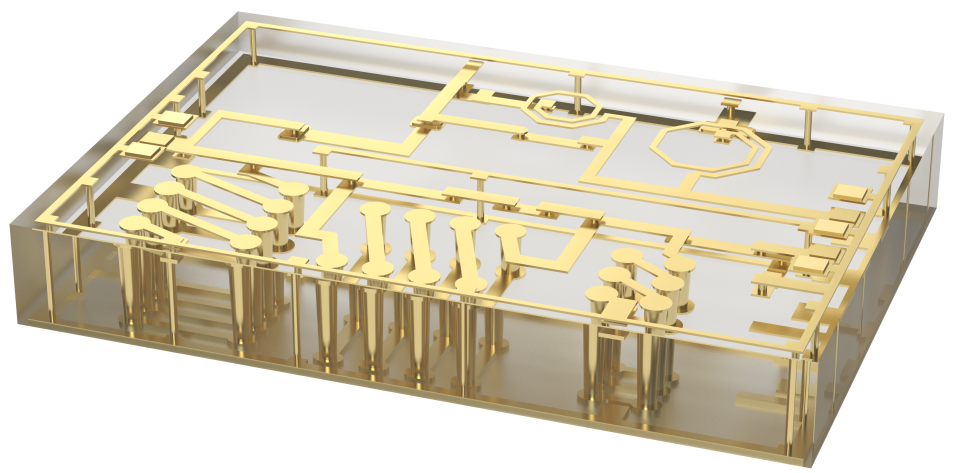

郑力强调,本轮发展的核心,在于先进封装正在经历的“精度革命”。他指出,这一变革并非单一指标提升,而是在“对准精度”“互连密度”“表面粗糙度”和“界面间隙”四个关键维度实现系统性跨越,构成原子级工艺演进的核心支撑。

首先是在对准精度上的跨越。他指出,例如,以混合键合为代表的高密度互连技术,正在把芯粒间互连从百级/千级每平方毫米推进到万级乃至更高水平。其次是在界面与表面控制能力上的突破。郑力指出,随着封装向高密度互联演进,表面粗糙度成为关键瓶颈之一。 当表面达到原子级平整度时,芯片之间可以在分子层面实现真正意义上的结合。

第三是在互联密度与连接方式上的跃迁。郑力表示,相较传统封装有限的互联能力,先进封装通过高密度布线与混合键合技术,大幅提升单位面积内的连接数量。在这种模式下,电气性能与信号完整性显著改善,为高性能计算与AI算力提供关键支撑。

“当精度进入原子级之后,整个制造逻辑就发生了变化。”郑力表示,这意味着芯片制造不再单纯依赖晶体管尺寸的缩小,而是转向通过系统结构优化来实现性能提升。

“这实际上是换了一条路。”郑力表示,原子级先进封装为异质异构集成提供了基础,使行业在接近极限时实现“柳暗花明又一村”的突破。

AI赋能与产业协同,推动先进封装新生态形成

在演讲中,郑力多次强调AI对先进封装的重要作用。他表示,随着工艺复杂度大幅提升,传统依赖工程师经验进行参数调优的方式已难以适应当前需求。

“现在的先进封装,很多场景已经必须依赖AI。”郑力指出,从设备层到生产现场,AI正在全面介入工艺开发与制造过程,通过实时数据采集、数据清洗以及数字孪生建模,实现对工艺的动态优化与决策支持。

与此同时,原子级封装技术也为AI系统能力的扩展提供支撑。例如依托原子级封装,实现数千甚至数万个AI芯片的超大规模互联,从而打破算力瓶颈。依托光电合封(CPO)技术,可实现光电器件与芯片的微系统集成,为下一代高性能计算系统提供了更高效的实现路径。

此外,产业链协同也在发生深刻变化。郑力表示,传统“设计—制造—封测”相对分离的模式正在被打破,各环节必须在系统级框架下协同推进。

在这一过程中,测试环节的重要性显著提升。他指出,在多芯片堆叠架构下,测试复杂度呈指数级增长,不仅测试时间大幅延长,误测、漏测等问题也更加突出,非破坏性检测技术正成为关键方向。

此外,在材料与载体方面,郑力提到以玻璃基板为代表的新技术路线正在加速推进。相比传统材料,玻璃在高频性能、成本及热匹配方面具有优势。

郑力最后总结指出,在后摩尔时代,先进封装正在从根本上重塑芯片制造逻辑。通过向原子级精度演进,并结合系统级集成与AI赋能,行业正在构建一条全新的发展路径。

“从晶体管微缩到系统级扩展,这是一次范式转变。”郑力表示,先进封装不仅为突破物理极限提供了解决方案,也为产业链带来了更广阔的发展空间。