JEDEC(固态技术协会)近期正式发布了HBM4标准。作为HBM3的升级版,HBM4进一步提升了数据处理速率,同时保持更高带宽、更高能效及每颗芯片/堆叠的容量等基本特征。随着AI模型和HPC高性能计算对更高带宽和更大容量内存技术需求不断增长,HBM4标准的推出将满足这些需求。SK海力士、三星和美光等内存厂商也将加速推出HBM4产品。

推进HBM4开发与量产

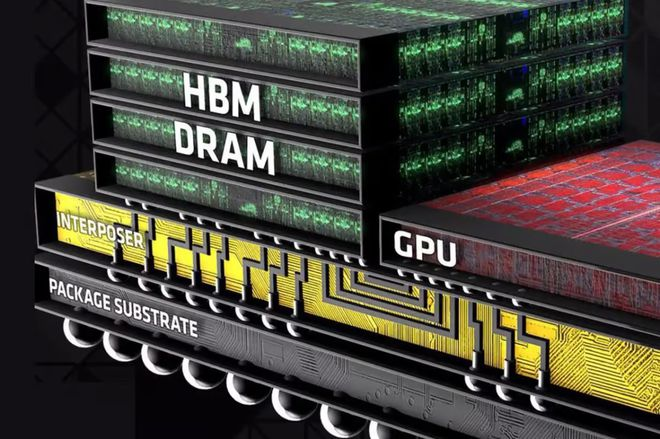

HBM4标准在带宽、通道数、功耗、容量等多方面都进行了改进。首先是带宽上的增加,通过2048bit接口提供高达8Gb/s的传输速度,总带宽提高至2TB/s。另一个重要升级是每个堆叠的独立通道数加倍,从16个通道(HBM3)增加到32个通道,每个通道包含2个伪通道。这为设计人员提供了更大的灵活性。

其次是容量上的提升。HBM4支持4层、8层、12层和16层DRAM堆栈。这些芯片密度可达24Gb或32Gb,可提供64GB(32Gb 16高)的更高立方体密度。

在能效提升方面,HBM4对一系列供应商特定电压给予支持,包括0.7V、0.75V、0.8V或0.9V的VDDQ(数据输出缓冲器电压)选项,以及1.0V或1.05V的VDDC(供应芯片核心电压)选项。这些调整有助于降低功耗并提高不同系统需求下的能效。

HBM4还与现有HBM3控制器兼容性,允许在各种应用中实现无缝集成和灵活性,并允许单个控制器在需要时与HBM3和HBM4配合使用。HBM4还集成定向刷新管理(DRFM),可增强行锤缓解(row-hammer)能力,并支持更强大的可靠性、可用性和可维护性功能(RAS)。

HBM4标准的正式落地,将推进HBM4的开发与量产。IDTechEx高级技术分析师Shababa Selim表示,HPC和AI工作负载经常会因为内存瓶颈而限制性能,这是因为CPU、GPU和其他AI加速器等处理器性能的发展超过了内存性能的发展。HBM是这类并行计算机架构的关键推动因素,许多GPU和加速器都使用HBM进行并行工作负载处理。

Selim表示,HBM的高带宽使其能够同时处理来自不同核心的多个内存请求,这对于GPU和加速器至关重要。根据IDTechEx的最新报告,预计到2035年HPC的HBM单位销量将比2024年增长15倍。

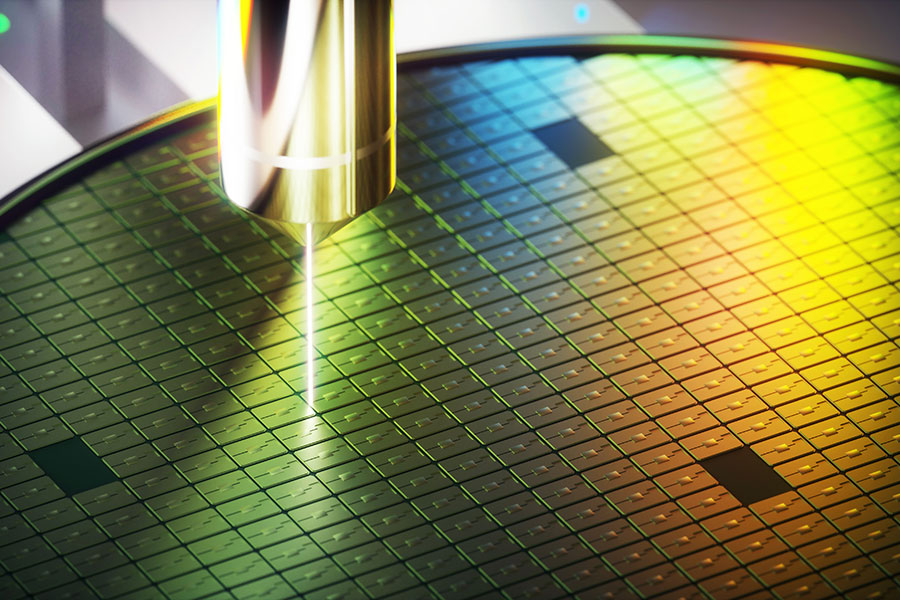

事实上,尽管HBM4标准刚于前不久正式发布,但相关厂商早在2024年已经展开样品的测试和设计。这是因为这些头部厂商都深度参与到JEDEC标准的制定当中,使其提前掌握技术方向,如三星在2024年就完成了16层混合键合堆叠验证。此外,英伟达、AMD等AI芯片厂商也需提前验证内存性能。

三大厂竞逐加剧

三星、SK海力士和美光都对HBM4给予了高度关注。HBM4标准的正式发布也加剧了三大内存制造商在产品开发与量产上的竞逐。

在HBM上,SK海力士占得头筹。其计划今年下半年开始生产HBM4 12Hi。据报道,HBM4 12Hi将搭载于英伟达下一代“Rubin”系列处理器中。目前,SK海力士已向英伟达供应HBM3E 12Hi,并已提供HBM4 12Hi样品。

SK海力士强调:“以引领HBM市场的技术竞争力和生产经验为基础,能够比原计划提早实现HBM4 12Hi的样品出货,并已开始与客户的验证流程。公司将在下半年完成量产准备,由此巩固在面向AI的新一代存储器市场领导地位。”

据韩媒报道,SK海力士已将HBM 4的测试良率提升至70%。测试产量是未来实际产量的指标,高测试良率可以确保进入实际量产时的生产效率。有业内人士评价称,“测试良率达到70%是一个非常好的成绩,量产后良率还可以进一步提升。”

三星电子在HBM3E市场竞争中落后于SK海力士,目前寄望于在HBM4上扭转劣势。三星芯片业务负责人全永铉表示,三星计划最早在今年第二季度供应HBM3E 12Hi,并计划在下半年生产HBM4芯片。

现在,三星电子将HBM4业务的重点放在了正在开发的10㎚级第6代(1c)DRAM上,计划在HBM4 12Hi产品中配备1c DRAM和逻辑芯片。如果能够稳步量产1c DRAM,有望在HBM4的产品性能上取得优势。SK海力士的HBM4配备的是1b DRAM。

美光则计划于2026 年量产上市HBM4。在2025财年第二季度财报电话会议上,美光总裁兼首席执行官Sanjay Mehrotra宣布这项计划。他表示,与HBM3E相比,美光的HBM4可将带宽提高60%以上。

PCIe 7.0、NVMe 2.1规范持续推进

JEDEC组织制订的其他存储芯片相关标准规范,如PCI-SIG、NVMe等也值得关注,对存储芯片的技术发展与落地有很大的作用。

在PCI-SIG标准方面,随着PCIe 5.0/6.0等高速接口的推出,存储芯片的数据传输速度将得到显著提升,这将对SSD主控芯片的性能提出更高的要求,推动SSD主控芯片产业向高性能方向发展。相比于 PCIe 6.0 规范,PCIe 7.0 规范的数据传输速率将再次倍增,达到 128 GT/s,大幅度高于 PCIe 6.0 的 64 GT/s 和 PCIe 5.0 的 32 GT/s。但PCIe 6.0/7.0 规范部署有所延迟。PCIe 6.0 深度一致性测试将于 2025 年启动,PCIe 7.0 的最终规格仍计划于 2025 年发布,但相应的 Live Compliance 计划已推迟到 2028 年。

NVMe是一种基于PCIe总线的高性能存储协议,专为基于PCIe总线的固态硬盘设计。NVMexpress组织在2024年8月7日宣布了三个新规格和八个更新规格的发布。新规格包括NVMe Boot规范、子系统本地内存命令集和计算程序命令集。更新内容则涵盖了NVMe 2.1基础规范、命令集规范(NVM命令集、ZNS命令集、键值命令集)、传输规范(PCIe传输、FC传输、RDMA传输和TCP传输)以及NVMe管理接口规范。这些更新和新规格旨在简化NVMe架构的开发流程,同时引入了适应现代计算环境的新功能,并且进一步加强了跨所有主要传输协议的NVMe技术支持。

评论

文明上网理性发言,请遵守新闻评论服务协议

登录参与评论

0/1000