1、英迪芯微“一种振荡电路”专利公布

2、钰泰半导体“LED驱动电路”专利公布

3、芯谷微电子“一种半导体封装设备及方法”专利公布

4、康芯威“一种存储装置的测试系统及其测试方法”专利公布

5、智芯微“非对称型混合多栅半导体器件及其制作方法、芯片”专利公布

1、英迪芯微“一种振荡电路”专利公布

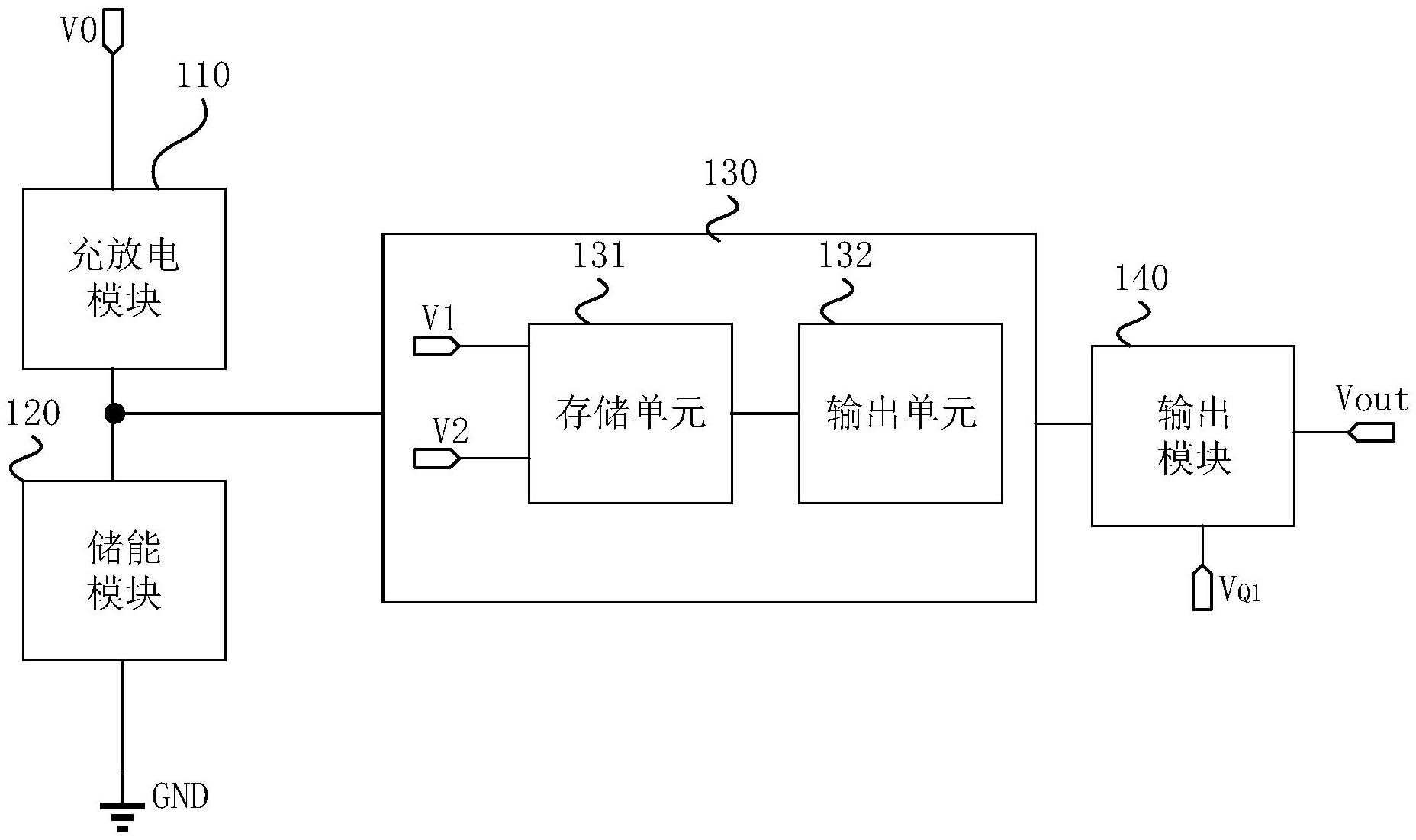

天眼查显示,无锡英迪芯微电子科技股份有限公司“一种振荡电路”专利公布,申请公布日为2025年2月28日,申请公布号为CN119543890A。

本发明公开了一种振荡电路。振荡电路包括充放电模块、储能模块、自归零比较模块和输出模块;自归零比较模块包括存储单元和输出单元;充放电模块与储能模块连接,充放电模块用于根据电源电压对储能模块进行充放电,以使储能模块输出三角波信号;存储单元接入第一阈值电压、第二阈值电压和输出单元的失调电压,输出单元用于在反馈电压为第二电平时,基于三角波信号与第一阈值电压的比较结果输出比较信号,在反馈电压为第一电平时,基于三角波信号与第二阈值电压的比较结果输出比较信号;输出模块与自归零比较模块连接,输出模块接入反馈电压,输出模块用于根据比较信号和反馈电压输出振荡信号。本发明的技术方案提升了振荡电路的可靠性和稳定性。

2、钰泰半导体“LED驱动电路”专利公布

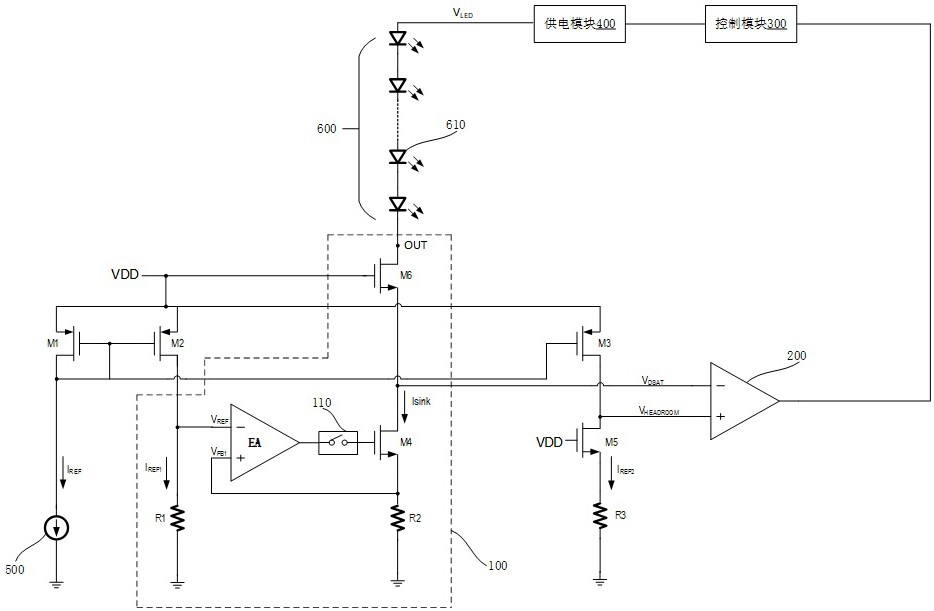

天眼查显示,钰泰半导体股份有限公司“LED驱动电路”专利公布,申请公布日为2025年2月28日,申请公布号为CN119545600A。

本发明涉及一种LED驱动电路,包括电流阱、比较器、控制模块、供电模块和采样电路,电流阱包括第一电阻、误差放大器、开关模块、第四晶体管、第六晶体管和第二电阻,采样电路包括第一电流源、第一晶体管、第二晶体管、第三晶体管、第五晶体管和第三电阻;开关模块用于通过脉冲宽度调制信号来实现周期性的开和关,以使第四晶体管的栅极与误差放大器的输出端周期性的接通和断开;控制模块用于根据比较器的输出信号向供电模块输出控制信号,以通过控制信号调整供电模块的输出电压。本发明的LED驱动电路,其电流阱的阱电压可跟随其最小阱电压变化,并与最小阱电压始终保持较小的差距,从而减小功耗,提高驱动效率。

3、芯谷微电子“一种半导体封装设备及方法”专利公布

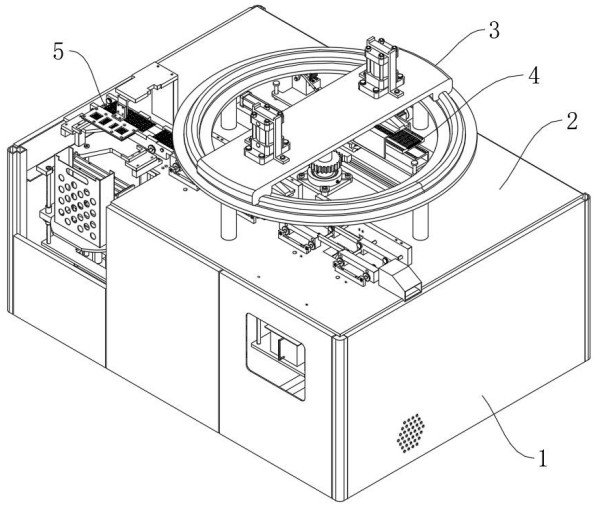

天眼查显示,合肥芯谷微电子股份有限公司“一种半导体封装设备及方法”专利公布,申请公布日为2025年2月28日,申请公布号为CN119525597A。

本发明公开了一种半导体封装设备及方法,涉及半导体器件技术领域,旨在解决半导体封装工艺中,切筋机持续的对半导体引线框架进行切割作业时,切割刀的刃口容易磨损、形状可能会发生变化,从而影响切割精度的技术问题,包括切筋机主体,切筋机主体包括操作台,操作台顶面布置有交替式切割组件和保养组件,保养组件包括升降板,升降板底面布置有升降组件,升降板顶面布置有往复平移组件和研磨组件。本发明具有两组半导体切割刀能够交替进行切割工作,使长时间工作的半导体切割刀能够进入闲置状态,另一组半导体切割刀进入工作状态,既保障了切割工作的持续进行,又能够通过研磨组件对闲置状态下的半导体切割刀进行研磨保养的优点。

4、康芯威“一种存储装置的测试系统及其测试方法”专利公布

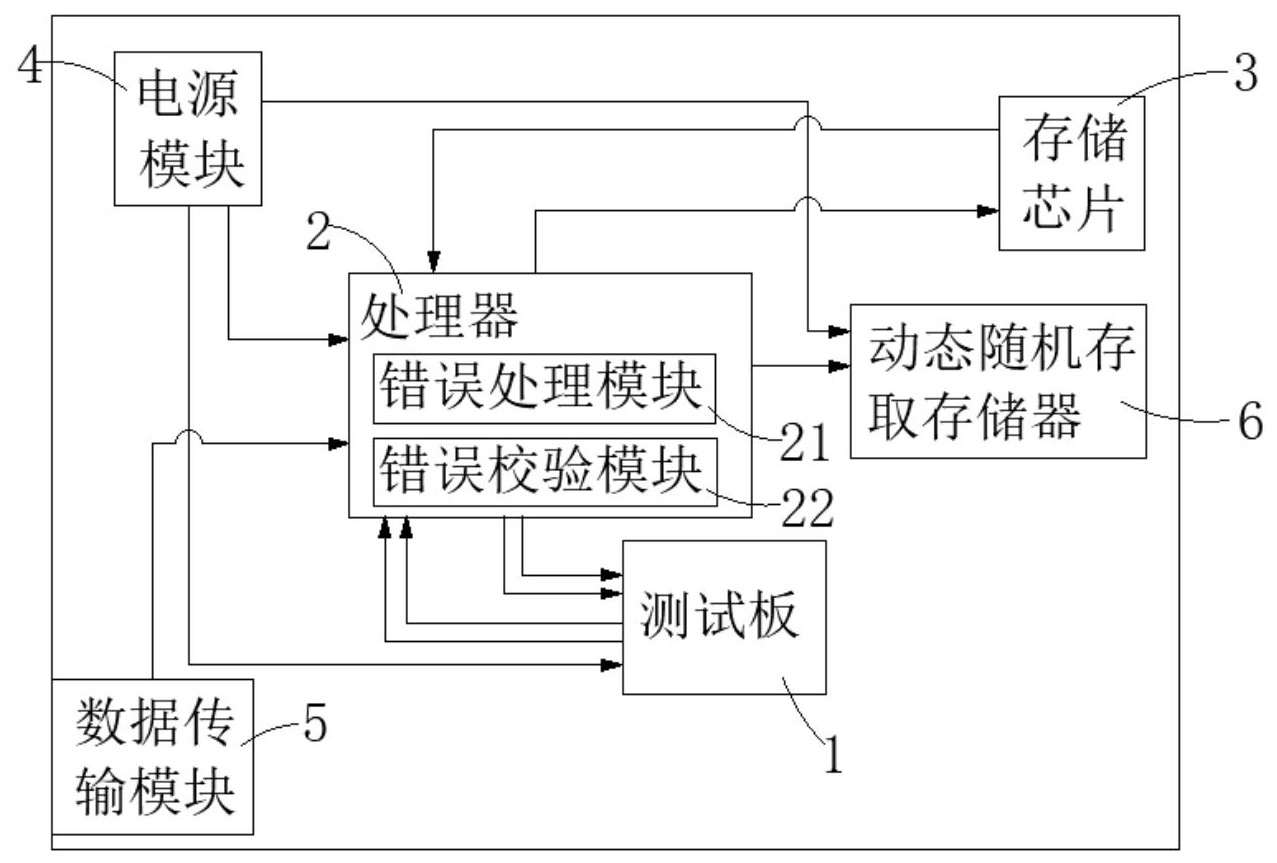

天眼查显示,合肥康芯威存储技术有限公司“一种存储装置的测试系统及其测试方法”专利公布,申请公布日为2025年2月28日,申请公布号为CN119541608A。

本发明提供一种存储装置的测试系统及其测试方法,涉及存储技术领域,包括:测试板,用以与待测存储器通信连接,以配置对应的测试参数;以及处理器,用以与所述测试板通信连接,且被配置为:在将消息数据写入至所述待测存储器前,使其生成发生不同读写校验错误的多个待测信息值,且在将各所述待测信息值依次写入至所述待测存储器中的重放保护内存块,以进行将各所述待测信息值至所述待测存储器的读写测试,得到测试结果。本发明提供的存储装置的测试系统及其测试方法,可以应用于存储器固件RPMB处理流程开发阶段,系统与固件对测稳定性及兼容性,具有简单易操作,RPMB类型配置丰富,测试覆盖度高等优点。

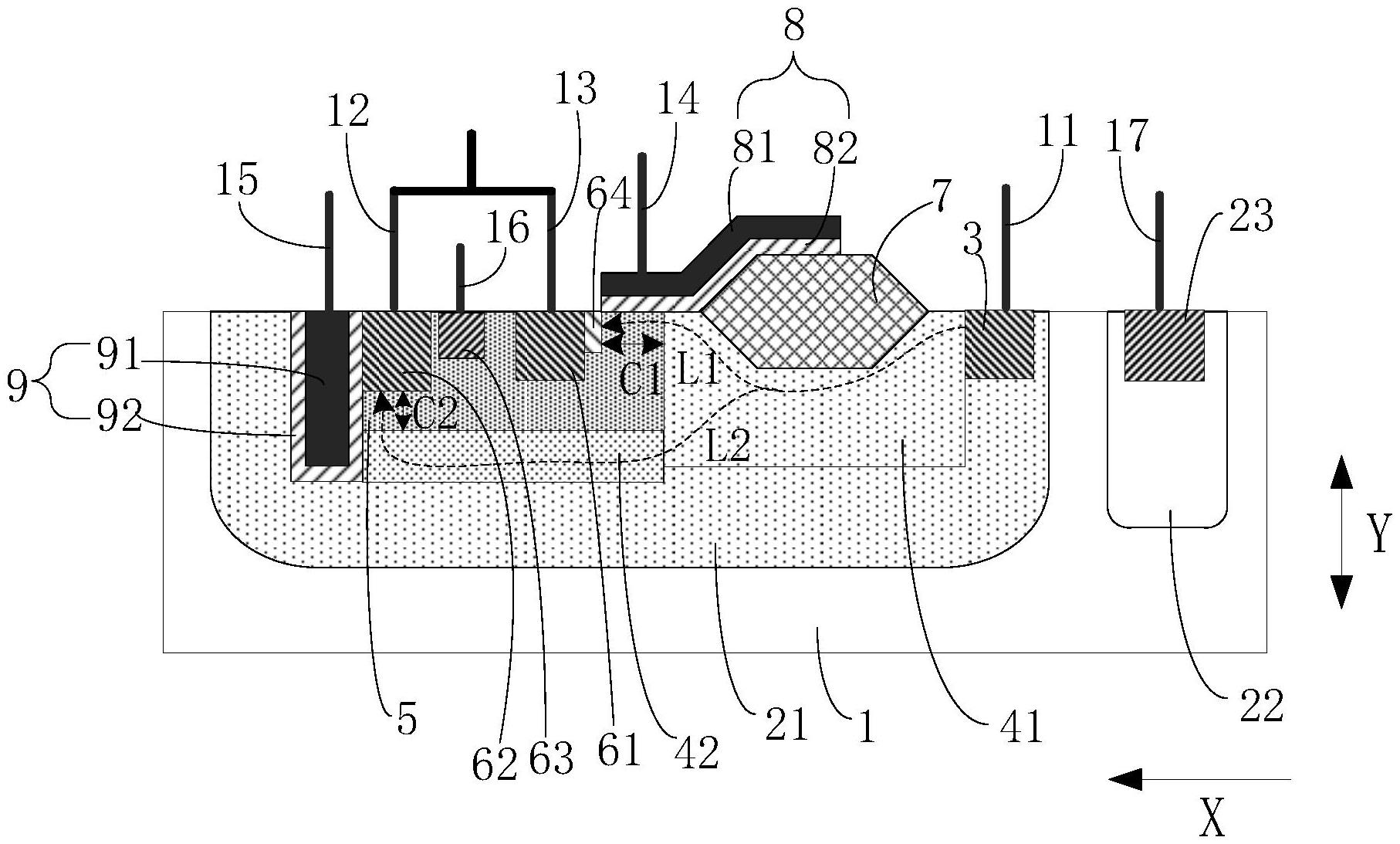

5、智芯微“非对称型混合多栅半导体器件及其制作方法、芯片”专利公布

天眼查显示,北京智芯微电子科技有限公司“非对称型混合多栅半导体器件及其制作方法、芯片”专利公布,申请公布日为2025年2月28日,申请公布号为CN119545855A。

本申请公开了一种非对称型混合多栅半导体器件及其制作方法、芯片,属于半导体技术领域。所述非对称型混合多栅半导体器件包括:衬底,包括第一高压阱区,第一高压阱区中设有沿目标方向依次连接的漏极区、第一漂移区和第二漂移区,第二漂移区的掺杂浓度大于第一漂移区的掺杂浓度;第二漂移区中的阱区中设有沿目标方向相间隔的第一源极区和第二源极区,第一源极区靠近第一漂移区一侧的阱区构成第一沟道区,第二源极区底部的阱区构成第二沟道区;第一栅极结构,覆盖第一沟道区;第二栅极结构,位于第一高压阱区内,且覆盖第二沟道区。本申请能够在提高器件的过电流能力的同时,维持了较小的器件面积,保证了器件集成度。

评论

文明上网理性发言,请遵守新闻评论服务协议

登录参与评论

0/1000